11.8 Cross-Probing from SmartTime to Chip View or Netlist Viewer

(Ask a Question)Cross-probing allows you to select a design object in one application and see the selection reflected in another application. When you cross-probe a design object from SmartTime to the Chip View/ Netlist View, you will better understand how the two applications interact with each other.

11.8.1 Cross-Probing from SmartTime to Chip View

(Ask a Question)With cross-probing, a timing path not meeting timing requirements may be fixed with relative ease when you see the less-than-optimal placement of the design object (in terms of timing requirement) in Chip Planner. Cross-probing from SmartTime to Chip Planner is available for the following design objects:

- Macros

- Ports

- Nets/Paths

- Complete Place and Route on the design.

- Open both SmartTime and Chip Planner.

11.8.1.1 Cross-Probing Examples

(Ask a Question)To cross-probe from SmartTime to Chip Planner, a design macro in the SmartTime is used as an example. You can download the example design files from the following location:

www.microchip.com/en-us/products/fpgas-and-plds/documentation

You can download the demo guide from the following location: www.microchip.com/en-us/application-notes/dg0852.html

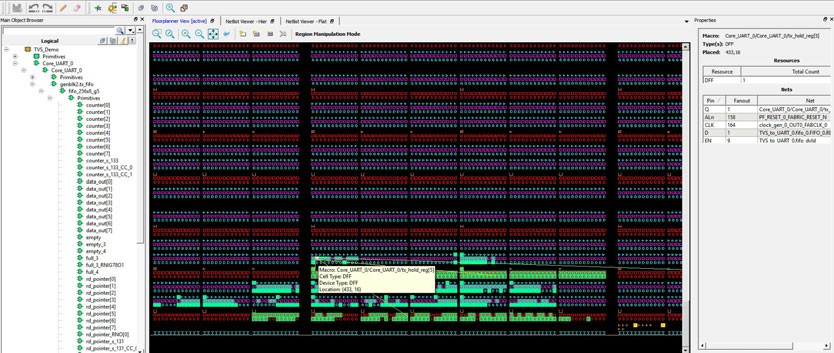

11.8.1.1.1 Design Macro Example

(Ask a Question)- Make sure that the design has successfully completed the Place and Route step.

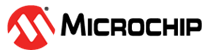

- Open SmartTime Maximum/Minimum Analysis view.

- Open Chip Planner.

-

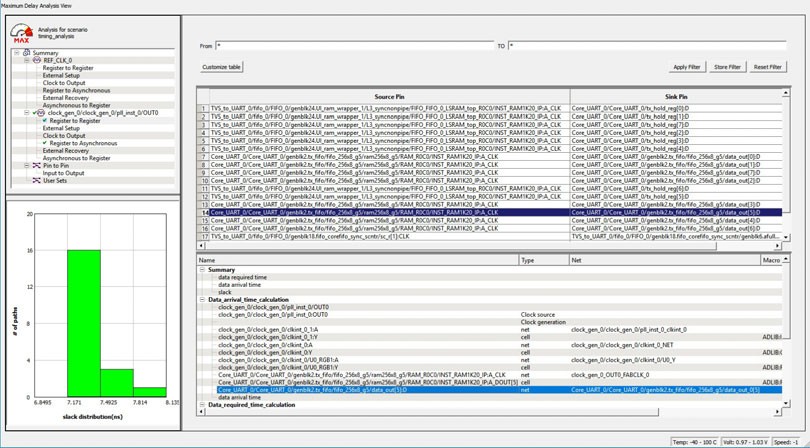

In the SmartTime Maximum Analysis view, right click the instance

ending in data_out[5] in the Timing Path Graph and choose Show in

Chip Planner. With cross-probing, that macro is selected in Chip Planner's

Logical view (zoom in to see the selected item) and highlighted in white in the

Floorplanner View. Zoom in to see the selected item. The Properties window in Chip

Planner displays the properties of the macro ending in data_out[5].

Note: The menu item Show in Chip Planner is grayed out if Chip Planner is not already open. You may need to zoom in to view the highlighted Q[2] macro in the Floorplanner View.

Figure 11-50 11-51. Cross-Probing the Macro Ending in data_out[5] in SmartTime View

Figure 11-50 11-51. Cross-Probing the Macro Ending in data_out[5] in Floorplanner View

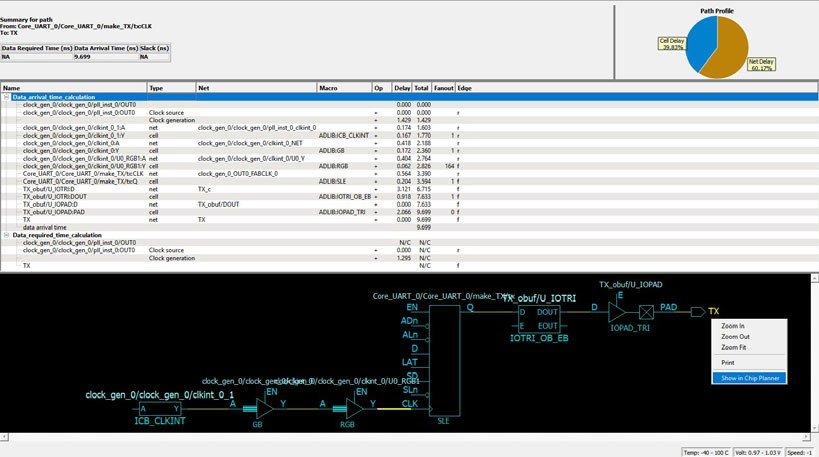

11.8.1.1.2 Timing Path Example

(Ask a Question)- Make sure the design completed the Place and Route step successfully.

- Open SmartTime Maximum/Minimum Analysis view.

- Open Chip Planner.

-

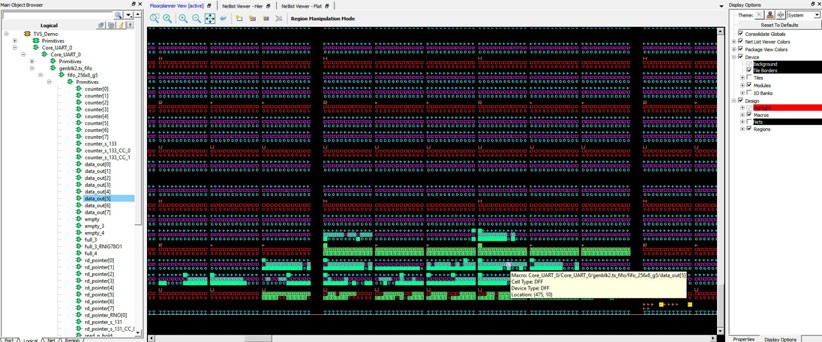

In the SmartTime Maximum/Minimum Analysis view, right click the macro

Core_UART_0/ Core_UART_0/tx_hold_reg[5] in the table and choose

Show Path in Chip Planner. There will be a net going from the macro

ending in tx_hold_reg[5] to the other macros such as PF_RESET_0, RAM1K20 and

RAM_R0C0 and local level global clock.

Note: If Chip Planner is not already open, the menu item in Show Path in Chip Planner is grayed out.

Figure 11-52. Cross-Probing - Timing Path (SmartTime View)

Figure 11-53. Cross-Probing - Timing Path (Floorplanner View)

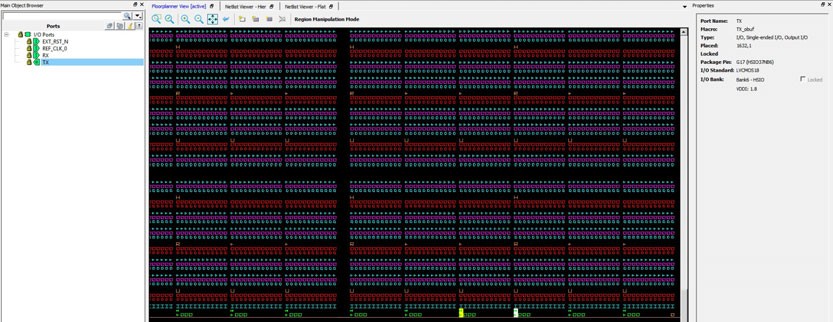

11.8.1.1.3 Port Example

(Ask a Question)- Make sure the design completed the Place and Route step successfully.

- Open the SmartTime Maximum/Minimum Analysis view.

- Open Chip Planner.

- In the SmartTime Maximum/Minimum Analysis view, right click the port TX in the Path and choose Show in Chip Planner. Note that the port “TX” is selected and highlighted in Chip Planner's Port view.

From the Properties View inside Chip Planner, you will find the following information about the Port “CLK” you are cross-probing:

- Port Type

- Port Placement Location (X-Y Coordinates)

- I/O Bank Number

- I/O Standard

- Pin Assignment

11.8.2 Cross-Probing from SmartTime to Netlist Viewer

(Ask a Question)To cross-probe from SmartTime to Netlist Viewer, perform the following steps:

- In Libero, complete the Place and Route step.

- Invoke the Chip Planner.

- In Chip Planner, select Netlist Viewer - Flat.

-

In the toolbar, turn on the zoom and center option:

.

- In the Design Flow window, open SmartTime.

- Open the Maximum/Minimum Delay Analysis view.

- To open the Timing Path display in SmartTime, click on a timing path.

-

Right-click a cell in the timing path display or a timing path in the SmartTime

table and select Show in Chip Planner.

Figure 11-56. Cross-Probe a Cell from SmartTime to Netlist Viewer Netlist Viewer shows the selected item and highlights it.Figure 11-57. Cross-Probed Cell in Netlist Viewer View Tip: Each time you click Show In Chip Planner action, the selected object is added to the list of objects previously selected on the Netlist Viewer canvas. To view all selected objects, click Zoom to Fit on the Netlist Viewer toolbar. In some cases, selected objects may be located on different pages of the canvas. To navigate between these pages, use the Previous Page and Next Page buttons. To view all selected objects on a single page, disable Page Splitting. -

To view the objects in the path of the net, right-click a net in the timing

path in the SmartTime table and select Show Path in Chip

Planner.

Figure 11-58. Cross-Probe a Net from SmartTime to Netlist Viewer Attention: Cross-probing a net from the timing path display to Netlist Viewer is not supported.Tip: You might want to Disable Page Splitting settings and click on Zoom to Fit to view all the selected items.Netlist Viewer shows the objects in the selected net path and highlights them.Figure 11-59. Cross-Probed Cell in the Path of the Net in Netlist Viewer View -

If desirable, add the highlighted objects of interest in the Netlist view to a

cone view, and add Drivers or Loads to the active cone view for debugging.

To clear all cross-probe objects and paths, click Clear Cross Probe from the top toolbar of the window.