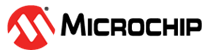

16.1.10 MACC_PA_BC_ROM

(Ask a Question)The MACC_PA_BC_ROM macro extends the functionality of the MACC_PA macro to provide a 16x18 ROM at the A input along with a pipelined output of B for cascading.

16.1.10.1 Features

(Ask a Question)The additional features of the MACC_PA_BC_ROM block are as follows:

- Selection of the A input from a 16 x 18 ROM.

- Additional pipelining of the B input for cascading to the next Math block or output to the fabric.

- Due to routing bandwidth limitations, either result P or B2 output can be used in the same MACC_PA_BC_ROM block.

16.1.10.2 Parameters

(Ask a Question)There is one parameter, INIT, to hold the 16x18 ROM content as a linear array. The first 18 bits is word 0, the next 18 bits is word 1, and so on.

| Parameter | Dimensions | Description |

|---|---|---|

| INIT | parameter [287:0] INIT = { 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0, 18'h0 }; | 16 x 18 ROM content specified in Verilog |

| INIT | generic map(INIT => ( B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”& B“00_0000_0000_0000_0000”) ) | 16 x 18 ROM content specified in VHDL |

PORT LIST

| Port Name | Direction | Type | Polarity | Description |

|---|---|---|---|---|

| DOTP | Input | Static | High | Dot-product mode. When DOTP = 1, MACC_PA_BC_ROM block performs Dot-product of two pairs of 9-bit operands. • SIMD must not be 1. • C[8:0] must be connected to CARRYIN. |

| SIMD | Input | Static | High | SIMD mode. When SIMD = 1, MACC_PA_BC_ROM block performs dual independent multiplication of two pairs of 9-bit operands.

|

| OVFL_CARRYOUT_SEL | Input | Static | High | Generate OVERFLOW or CARRYOUT with result P.

|

| CLK | Input | Dynamic | Rising edge | Clock for A, B, C, CARRYIN, D, P, OVFL_CARRYOUT, ARSHFT17, CDIN_FDBK_SEL, PASUB and SUB registers. |

| AL_N | Input | Dynamic | Low | Asynchronous load for A, B, B2, P, OVFL_CARRYOUT, ARSHFT17, CDIN_FDBK_SEL, PASUB and SUB registers. Connect to 1, if none are registered. When asserted, A, B, P and OVFL_CARRYOUT registers are loaded with zero, while the ARSHFT17, CDIN_FDBK_SEL, PASUB and SUB registers are loaded with the complementary value of the respective _AD_N. |

| USE_ROM | Input | Static (virtual) | High | Selection for operand A.

|

| ROM_ADDR[3:0] | Input | Dynamic | High | Address of ROM data for operand A when USE_ROM = 1. |

| A[17:0] | Input | Static | High | Input data for operand A when USE_ROM = 0. |

| A_BYPASS | Input | Dynamic | High | Bypass data A registers. Connect to 1, if not registered. See Table 16-146. |

| A_SRST_N | Input | Dynamic | Low | Synchronous reset for data A registers.

Connect to 1, if not registered. See Table 16-146. |

| A_EN | Input | Dynamic | High | Enable for data A registers. Connect to 1, if not registered. See Table 16-146. |

| B[17:0] | Input | Dynamic | High | Input data B to Pre-adder with data D. |

| B_BYPASS | Input | Static | High | Bypass data B registers. Connect to 1, if not registered. See Table 16-146. |

| B_SRST_N | Input | Dynamic | Low | Synchronous reset for data B registers. Connect to 1, if not registered. See Table 16-146. |

| B_EN | Input | Dynamic | High | Enable for data B registers. Connect to 1, if not registered. See Table 16-146. |

| B2[17:0] | Output | Dynamic | High | Pipelined output of input data B. Result P must be floating when B2 is used. |

| B2_BYPASS | Input | Static | High | Bypass data B2 registers. Connect to 1, if not registered. See Table 16-146 |

| B2_SRST_N | Input | Dynamic | Low | Synchronous reset for data B2 registers. Connect to 1, if not registered. See Table 16-146. |

| B2_EN | Input | Dynamic | High | Enable for data B2 registers. Connect to 1, if not registered. See Table 16-146. |

| BCOUT[17:0] | Output | Cascade | High | Cascade output of B2. Value of BCOUT is the same as B2. The entire bus must either be dangling or drive an entire B input of another MACC_PA or MACC_PA_BC_ROM block. |

| D[17:0] | Input | Dynamic | High | Input data D to Pre-adder with data B. When SIMD = 1, connect D[8:0] to 0. |

| D_BYPASS | Input | Static | High | Bypass data D registers. Connect to 1, if not registered. See Table 16-147. |

| D_ARST_N | Input | Dynamic | Low | Asynchronous reset for data D registers. Connect to 1, if not registered. See Table 16-147. |

| D_SRST_N | Input | Dynamic | Low | Synchronous reset for data D registers. Connect to 1, if not registered. See Table 16-147. |

| D_EN | Input | Dynamic | High | Enable for data D registers. Connect to 1, if not registered. See Table 16-147. |

| CARRYIN | Input | Dynamic | High | CARRYIN for input data C. |

| C[47:0] | Input | Dynamic | High | Input data C. When DOTP = 1, connect C[8:0] to CARRYIN. When SIMD = 1, connect C[8:0] to 0. |

| C_BYPASS | Input | Static | High | Bypass CARRYIN and C registers. Connect to 1, if not registered. See Table 16-147. |

| C_ARST_N | Input | Dynamic | Low | Asynchronous reset for CARRYIN and C registers. Connect to 1, if not registered. See Table 16-147. |

| C_SRST_N | Input | Dynamic | Low | Synchronous reset for CARRYIN and C registers. Connect to 1, if not registered. See Table 16-147. |

| C_EN | Input | Dynamic | High | Enable for CARRYIN and C registers. Connect to 1, if not registered. See Table 16-147. |

| CDIN[47:0] | Input | Cascade | High | Cascaded input for operand E. The entire bus must be driven by an entire CDOUT of another MACC_PA or MAC_PA_BC_ROM block. In Dot-product mode, the driving CDOUT must also be generated by a MACC_PA or MAC_PA_BC_ROM block in Dot-product mode. Refer to Table 16-142 to see how CDIN is propagated to operand E. |

| P[47:0] | Output | High | Result data. See Table 16-143. B2 output must be floating when P is used. | |

| OVFL_CARRYOUT | Output | High | OVERFLOW or CARRYOUT. See Table 16-144. | |

| P_BYPASS | Input | Static | High | Bypass P and OVFL_CARRYOUT registers. Connect

to 1, if not registered. See Table 16-146. P_BYPASS must be 0 when CDIN_FDBK_SEL[0] = 1. See Table 16-142. |

| P_SRST_N | Input | Dynamic | Low | Synchronous reset for P and OVFL_CARRYOUT registers. Connect to 1, if not registered. See Table 16-146. |

| P_EN | Input | Dynamic | High | Enable for P and OVFL_CARRYOUT registers. Connect to 1, if not registered. See Table 16-146. |

| CDOUT[47:0] | Output | Cascade | High | Cascade output of result P. See Table 16-143. Value of CDOUT is the same as P. The entire bus must either be dangling or drive an entire CDIN of another MACC_PA or MAC_PA_BC_ROM block incascaded mode. |

| PASUB | Input | Dynamic | High | Subtract operation for Pre-adder of B and D. |

| PASUB_BYPASS | Input | Static | High | Bypass PASUB register. Connect to 1, if not registered. See Table 16-145. |

| PASUB_AD_N | Input | Static | Low | Asynchronous load data for PASUB register. See Table 16-145. |

| PASUB_SL_N | Input | Dynamic | Low | Synchronous load for PASUB register. Connect

to 1, if not registered. See Table 16-145. |

| PASUB_SD_N | Input | Static | Low | Synchronous load data for PASUB register. See |

| PASUB_EN | Input | Dynamic | High | Enable for PASUB register. Connect to 1, if not registered. See Table 16-145. |

| CDIN_FDBK_SEL[1:0] | Input | Dynamic | High | Select CDIN, P or 0 for operand E. See Table 16-142. |

| CDIN_FDBK_SEL_BYPASS | Input | Static | High | Select CDIN, P or 0 for operand E. See Table 16-142. |

| CDIN_FDBK_SEL_AD_N [1:0] | Input | Static | Low | Asynchronous load data for CDIN_FDBK_SEL register. See Table 16-145. |

| CDIN_FDBK_SEL_SL_N | Input | Dynamic | Low | Synchronous load for CDIN_FDBK_SEL register. Connect to 1, if not registered. See Table 16-145. |

| CDIN_FDBK_SEL_SD_N [1:0] | Input | Static | Low | Synchronous load data for CDIN_FDBK_SEL register. See Table 16-145. |

| CDIN_FDBK_SEL_EN | Input | Dynamic | High | Enable for CDIN_FDBK_SEL register. Connect to 1, if not registered. See Table 16-145. |

| ARSHFT17 | Input | Dynamic | High | Arithmetic right-shift for operand E. When asserted, a 17-bit arithmetic right-shift is performed on operand E. Refer to Table 16-142 to see how operand E is obtained from P, CDIN or 0. When SIMD = 1, ARSHFT17 must be 0. |

| ARSHFT17_BYPASS | Input | Static | High | Bypass ARSHFT17 register. Connect to 1, if not registered. See Table 16-145. |

| ARSHFT17_AD_N | Input | Static | Low | Asynchronous load data for ARSHFT17 register. See Table 16-145. |

| ARSHFT17_SL_N | Input | Dynamic | Low | Synchronous load for ARSHFT17 register. Connect to 1, if not registered. See Table 16-145. |

| ARSHFT17_SD_N | Input | Static | Low | Synchronous load data for ARSHFT17 register. See Table 16-145. |

| ARSHFT17_EN | Input | Dynamic | High | Enable for ARSHFT17 register. Connect to 1, if not registered. See Table 16-145. |

| SUB | Input | Dynamic | High | Subtract operation. |

| SUB_BYPASS | Input | Static | High | Bypass SUB register. Connect to 1, if not registered. See Table 16-145. |

| SUB_AD_N | Input | Static | Low | Asynchronous load data for SUB register. See Table 16-145. |

| SUB_SL_N | Input | Dynamic | Low | Synchronous load for SUB register. Connect to 1, if not registered. Table 16-145. |

| SUB_SD_N | Input | Static | Low | Synchronous load data for SUB register. See Table 16-145. |

| SUB_EN | Input | Dynamic | High | Enable for SUB register. Connect to 1, if not registered. See Table 16-145. |