1.1 Macrocell (MC) Features

The ATF1500 and ATF15XX devices have distinct features for each macrocell, as detailed in Table 1-2.

| ATF1500 Macrocell | ATF15XX Macrocell |

|---|---|

|

Global or product-term controlled Output Enable originate from the Input pins |

Global (GOE0-GOE5) or product-term controlled Output Enable originate from the switch matrix |

|

Global or product-term controlled Reset inputs |

Global or product-term controlled Reset inputs |

|

Global or product-term controlled clock inputs |

3 global clocks or product-term clock input |

|

Product-term controlled Clock Enable and Preset inputs |

Product-term controlled Clock Enable and Preset inputs |

|

5 product terms per MC |

5 product terms per MC |

|

Foldback and cascade logic |

Foldback and cascade logic |

|

Independently configurable D/T/L flip-flop |

Independently configurable D/T/L flip-flop |

|

Combinatorial Output with a Buried Register option |

Combinatorial Output with a Buried Register option or Buried Combinatorial Output with Registered Output |

|

Pin-controlled or Automatic Power-Down Control options |

Pin-controlled or Automatic Power-Down Control options |

|

Slew rate control on each output |

Slew rate control on each output |

|

Programmable pin-keeper circuits |

Programmable pin-keeper circuits |

|

The ATF1500A is a non-ISP device |

4 JTAG port pins that allow for In-System Programming (ISP) |

|

Open collector outputs | |

|

Fast input from the I/O pin |

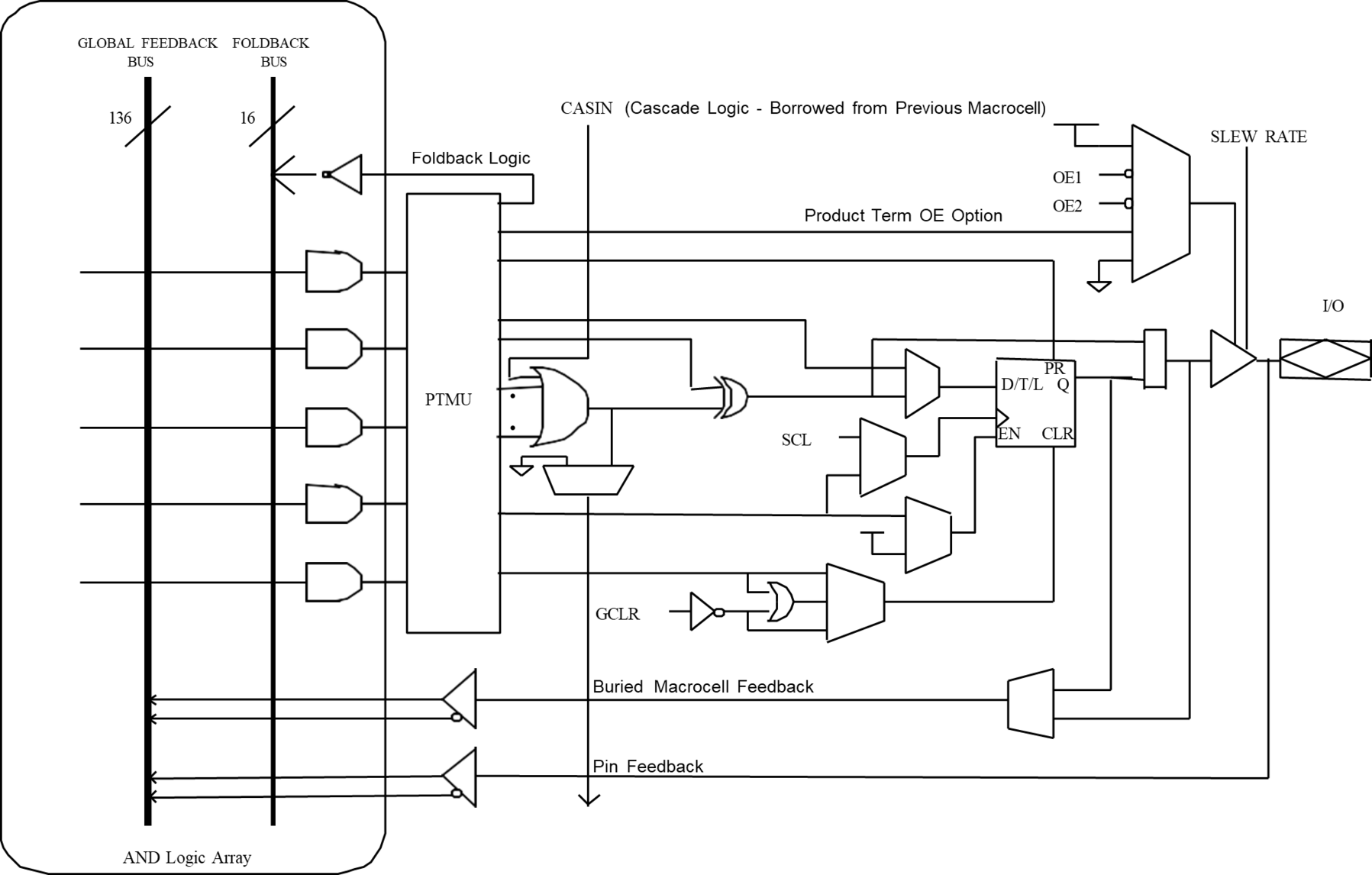

Figure 1 and Figure 1-4 illustrate the MC architectures for the ATF15xx and ATF1500 devices. The MC architecture is the same for the ATF1502, ATF1504 and ATF1508 devices, and it differs slightly from that of the ATF1500.