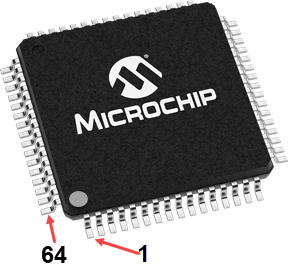

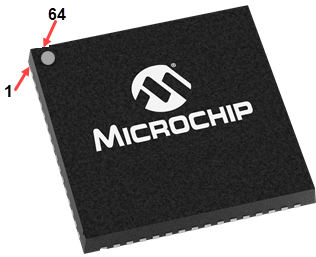

4.3 64-pin VQFN and 64-pin TQFP

| 64-pin VQFN and 64-pin TQFP (Top View )(1) | |

|---|---|

|

PIC32CM5164JH00064 PIC32CM2532JH00064 PIC32CM5164JH01064 PIC32CM2532JH01064 |

|

| |

|

Note:

| |

| Pin number | Pin Name | Peripheral Functions | Supply | Reset state | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| A | B | C | D | E | F | G | H | I | J | K | |||||||||

| EIC | REF | ADCO | ADC1 | AC | DAC | SERCOM | SERCOM | TC/TCC | TC/TCC | CAN (1), PDEC | AC, GCLK | CCL | PDEC | PTC | |||||

| 1 | PA00, XIN32 | EXTINT[0] | SERCOM1/PAD[0] | TCC2/WO[0] | TC7/WO[0] | CMP[2] | AVDD | I/O, HI-Z | |||||||||||

| 2 | PA01, XOUT32 | EXTINT[1] | SERCOM1/PAD[1] | TCC2/WO[1] | TC7/WO[1] | CMP[3] | AVDD | I/O, HI-Z | |||||||||||

| 3 | PA02 | EXTINT[2] | AIN[0] | AIN[4] | VOUT | Y[0], DS[0] | AVDD | I/O, HI-Z | |||||||||||

| 4 | PA03 | EXTINT[3] | VREFA | AIN[1] | AIN[5] | Y[1], DS[1] | AVDD | I/O, HI-Z | |||||||||||

| 5 | PB04 | EXTINT[4] | AIN[6] | Y[10], DS[10] | AVDD | I/O, HI-Z | |||||||||||||

| 6 | PB05 | EXTINT[5] | AIN[7] | AIN[6] | Y[11], DS[11] | AVDD | I/O, HI-Z | ||||||||||||

| 7 | AVSS | ||||||||||||||||||

| 8 | AVDD | ||||||||||||||||||

| 9 | PB06 | EXTINT[6] | AIN[8] | AIN[7] | IN[6] | Y[12], DS[12] | AVDD | I/O, HI-Z | |||||||||||

| 10 | PB07 | EXTINT[7] | AIN[9] | IN[7] | Y[13], DS[13] | AVDD | I/O, HI-Z | ||||||||||||

| 11 | PB08 | EXTINT[8] | AIN[2] | AIN[4] | SERCOM4/PAD[0] | TC0/WO[0] | IN[8] | Y[14], DS[14] | AVDD | I/O, HI-Z | |||||||||

| 12 | PB09 | EXTINT[9] | AIN[3] | AIN[5] | SERCOM4/PAD[1] | TC0/WO[1] | OUT[2] | Y[15], DS[15] | AVDD | I/O, HI-Z | |||||||||

| 13 | PA04 | EXTINT[4] | AIN[4] | AIN[0] | SERCOM0/PAD[0] | TCC0/WO[0] | TC5/WO[0] | IN[0] | Y[2], DS[2] | AVDD | I/O, HI-Z | ||||||||

| 14 | PA05 | EXTINT[5] | AIN[5] | AIN[1] | SERCOM0/PAD[1] | TCC0/WO[1] | TC5/WO[1] | IN[1] | Y[3], DS[3] | AVDD | I/O, HI-Z | ||||||||

| 15 | PA06 | EXTINT[6] | AIN[6] | AIN[2] | SERCOM0/PAD[2] | TCC1/WO[0] | TC6/WO[0] | IN[2] | Y[4], DS[4] | AVDD | I/O, HI-Z | ||||||||

| 16 | PA07 | EXTINT[7] | AIN[7] | AIN[3] | SERCOM0/PAD[3] | TCC1/WO[1] | TC6/WO[1] | OUT[0] | Y[5], DS[5] | AVDD | I/O, HI-Z | ||||||||

| 17 | PA08 | NMI | AIN[8] | AIN[10] | SERCOM0/PAD[0] | SERCOM2/PAD[0] | TCC0/WO[0] | TCC1/WO[2] | IN[3] | QDI[0] | X[0], Y[16], DS[16] | VDDIO | I/O, HI-Z | ||||||

| 18 | PA09 | EXTINT[9] | AIN[9] | AIN[11] | SERCOM0/PAD[1] | SERCOM2/PAD[1] | TCC0/WO[1] | TCC1/WO[3] | IN[4] | QDI[1] | X[1], Y[17], DS[17] | VDDIO | I/O, HI-Z | ||||||

| 19 | PA10 | EXTINT[10] | AIN[10] | SERCOM0/PAD[2] | SERCOM2/PAD[2] | TCC1/WO[0] | TCC0/WO[2] | GCLK/IO[4] | IN[5] | QDI[2] | X[2], Y[18], DS[18] | VDDIO | I/O, HI-Z | ||||||

| 20 | PA11 | EXTINT[11] | AIN[11] | SERCOM0/PAD[3] | SERCOM2/PAD[3] | TCC1/WO[1] | TCC0/WO[3] | GCLK/IO[5] | OUT[1] | X[3], Y[19], DS[19] | VDDIO | I/O, HI-Z | |||||||

| 21 | VDDIO | ||||||||||||||||||

| 22 | GND | ||||||||||||||||||

| 23 | PB10 | EXTINT[10] | SERCOM4/PAD[2] | TC1/WO[0] | TCC0/WO[4] | CAN1/TX | GCLK/IO[4] | IN[5] | VDDIO | I/O, HI-Z | |||||||||

| 24 | PB11 | EXTINT[11] | SERCOM4/PAD[3] | TC1/WO[1] | TCC0/WO[5] | CAN1/RX | GCLK/IO[5] | OUT[1] | VDDIO | I/O, HI-Z | |||||||||

| 25 | PB12 | EXTINT[12] | SERCOM4/PAD[0] | TC0/WO[0] | TCC0/WO[6] | GCLK/IO[6] | X[12], Y[28], DS[28] | VDDIO | I/O, HI-Z | ||||||||||

| 26 | PB13 | EXTINT[13] | SERCOM4/PAD[1] | TC0/WO[1] | TCC0/WO[7] | GCLK/IO[7] | X[13], Y[29], DS[29] | VDDIO | I/O, HI-Z | ||||||||||

| 27 | PB14 | EXTINT[14] | SERCOM4/PAD[2] | TC1/WO[0] | TC7/WO[0] | CAN1/TX | GCLK/IO[0] | IN[9] | X[14], Y[30], DS[30] | VDDIO | I/O, HI-Z | ||||||||

| 28 | PB15 | EXTINT[15] | SERCOM4/PAD[3] | TC1/WO[1] | TC7/WO[1] | CAN1/RX | GCLK/IO[1] | IN[10] | X[15], Y[31], DS[31] | VDDIO | I/O, HI-Z | ||||||||

| 29 | PA12 | EXTINT[12] | SERCOM2/PAD[0] | SERCOM4/PAD[0] | TCC2/WO[0] | TCC0/WO[6] | CMP[0] | VDDIO | I/O, HI-Z | ||||||||||

| 30 | PA13 | EXTINT[13] | SERCOM2/PAD[1] | SERCOM4/PAD[1] | TCC2/WO[1] | TCC0/WO[7] | CMP[1] | VDDIO | I/O, HI-Z | ||||||||||

| 31 | PA14, XIN | EXTINT[14] | SERCOM2/PAD[2] | SERCOM4/PAD[2] | TC4/WO[0] | TCC0/WO[4] | GCLK/IO[0] | VDDIO | I/O, HI-Z | ||||||||||

| 32 | PA15, XOUT | EXTINT[15] | SERCOM2/PAD[3] | SERCOM4/PAD[3] | TC4/WO[1] | TCC0/WO[5] | GCLK/IO[1] | VDDIO | I/O, HI-Z | ||||||||||

| 33 | GND | ||||||||||||||||||

| 34 | VDDIO | ||||||||||||||||||

| 35 | PA16 | EXTINT[0] | SERCOM1/PAD[0] | SERCOM3/PAD[0] | TCC2/WO[0] | TCC0/WO[6] | QDI[0] | GCLK/IO[2] | IN[0] | X[4], Y[20], DS[20] | VDDIO | I/O, HI-Z | |||||||

| 36 | PA17 | EXTINT[1] | SERCOM1/PAD[1] | SERCOM3/PAD[1] | TCC2/WO[1] | TCC0/WO[7] | QDI[1] | GCLK/IO[3] | IN[1] | X[5], Y[21], DS[21] | VDDIO | I/O, HI-Z | |||||||

| 37 | PA18 | EXTINT[2] | SERCOM1/PAD[2] | SERCOM3/PAD[2] | TC4/WO[0] | TCC0/WO[2] | QDI[2] | CMP[0] | IN[2] | X[6], Y[22], DS[22] | VDDIO | I/O, HI-Z | |||||||

| 38 | PA19 | EXTINT[3] | SERCOM1/PAD[3] | SERCOM3/PAD[3] | TC4/WO[1] | TCC0/WO[3] | CMP[1] | OUT[0] | X[7], Y[23], DS[23] | VDDIO | I/O, HI-Z | ||||||||

| 39 | PB16 | EXTINT[0] | SERCOM5/PAD[0] | TC2/WO[0] | TCC0/WO[4] | GCLK/IO[2] | IN[11] | VDDIO | I/O, HI-Z | ||||||||||

| 40 | PB17 | EXTINT[1] | SERCOM5/PAD[1] | TC2/WO[1] | TCC0/WO[5] | GCLK/IO[3] | OUT[3] | VDDIO | I/O, HI-Z | ||||||||||

| 41 | PA20 | EXTINT[4] | SERCOM5/PAD[2] | SERCOM3/PAD[2] | TC3/WO[0] | TCC0/WO[6] | GCLK/IO[4] | X[8], Y[24], DS[24] | VDDIO | I/O, HI-Z | |||||||||

| 42 | PA21 | EXTINT[5] | SERCOM5/PAD[3] | SERCOM3/PAD[3] | TC3/WO[1] | TCC0/WO[7] | GCLK/IO[5] | X[9], Y[25], DS[25] | VDDIO | I/O, HI-Z | |||||||||

| 43 | PA22 | EXTINT[6] | SERCOM3/PAD[0] | SERCOM5/PAD[0] | TC0/WO[0] | TCC0/WO[4] | GCLK/IO[6] | IN[6] | X[10], Y[26], DS[26] | VDDIO | I/O, HI-Z | ||||||||

| 44 | PA23 | EXTINT[7] | SERCOM3/PAD[1] | SERCOM5/PAD[1] | TC0/WO[1] | TCC0/WO[5] | GCLK/IO[7] | IN[7] | X[11], Y[27], DS[27] | VDDIO | I/O, HI-Z | ||||||||

| 45 | PA24 | EXTINT[12] | SERCOM3/PAD[2] | SERCOM5/PAD[2] | TC1/WO[0] | TCC1/WO[2] | CAN0/TX | CMP[2] | IN[8] | VDDIO | I/O, HI-Z | ||||||||

| 46 | PA25 | EXTINT[13] | SERCOM3/PAD[3] | SERCOM5/PAD[3] | TC1/WO[1] | TCC1/WO[3] | CAN0/RX | CMP[3] | OUT[2] | VDDIO | I/O, HI-Z | ||||||||

| 47 | GND | ||||||||||||||||||

| 48 | VDDIO | ||||||||||||||||||

| 49 | PB22 | EXTINT[6] | SERCOM5/PAD[2] | TC3/WO[0] | CAN0/TX | GCLK/IO[0] | IN[0] | VDDIO | I/O, HI-Z | ||||||||||

| 50 | PB23 | EXTINT[7] | SERCOM5/PAD[3] | TC3/WO[1] | CAN0/RX | GCLK/IO[1] | OUT[0] | VDDIO | I/O, HI-Z | ||||||||||

| 51 | PA27 | EXTINT[15] | GCLK/IO[0] | VDDIN | I/O, HI-Z | ||||||||||||||

| 52 | RESET | VDDIN | I, PU | ||||||||||||||||

| 53 | PA28 | EXTINT[8] | GCLK/IO[0] | VDDIN | I/O, HI-Z | ||||||||||||||

| 54 | GND | ||||||||||||||||||

| 55 | VDDCORE | ||||||||||||||||||

| 56 | VDDIN | ||||||||||||||||||

| 57 | PA30, SWCLK | EXTINT[10] | SERCOM1/PAD[2] | TCC1/WO[0] | SWCLK | GCLK/IO[0] | IN[3] | VDDIN | SWCLK, I | ||||||||||

| 58 | PA31, SWDIO | EXTINT[11] | SERCOM1/PAD[3] | TCC1/WO[1] | OUT[1] | VDDIN | I/O, HI-Z | ||||||||||||

| 59 | PB30 | EXTINT[14] | SERCOM5/PAD[0] | TCC0/WO[0] | TCC1/WO[2] | CMP[2] | VDDIN | I/O, HI-Z | |||||||||||

| 60 | PB31 | EXTINT[15] | SERCOM5/PAD[1] | TCC0/WO[1] | TCC1/WO[3] | CMP[3] | VDDIN | I/O, HI-Z | |||||||||||

| 61 | PB00 | EXTINT[0] | AIN[0] | SERCOM5/PAD[2] | TC3/WO[0] | TC6/WO[0] | IN[1] | Y[6], DS[6] | AVDD | I/O, HI-Z | |||||||||

| 62 | PB01 | EXTINT[1] | AIN[1] | SERCOM5/PAD[3] | TC3/WO[1] | TC6/WO[1] | IN[2] | Y[7], DS[7] | AVDD | I/O, HI-Z | |||||||||

| 63 | PB02 | EXTINT[2] | AIN[2] | SERCOM5/PAD[0] | TC2/WO[0] | TC5/WO[0] | OUT[0] | Y[8], DS[8] | AVDD | I/O, HI-Z | |||||||||

| 64 | PB03 | EXTINT[3] | AIN[3] | SERCOM5/PAD[1] | TC2/WO[1] | TC5/WO[1] | Y[9], DS[9] | AVDD | I/O, HI-Z | ||||||||||

|

Note:

| |||||||||||||||||||