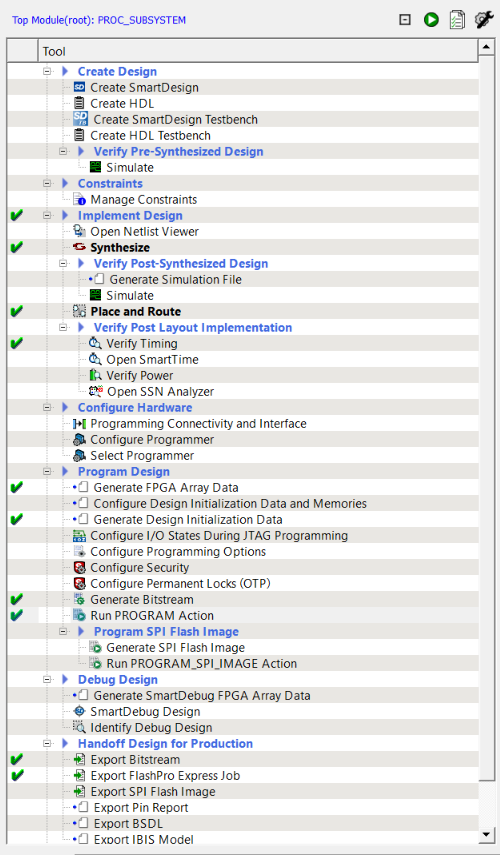

2 Libero Design Flow

(Ask a Question)The Libero design flow involves running the following processes in the Libero SoC PolarFire:

- Synthesize

- Place and Route

- Verify Timing

- Generate FPGA Array Data

- Configure Design Initialization Data and Memories

- Configure Programming Options

- Generate Bitstream

- Run PROGRAM Action

- Export FlashPro Express JobImportant: To initialize the TCM in PolarFire using the system controller, a local parameter l_cfg_hard_tcm0_en, in the

miv_rv32_subsys_pkg.vfile should be changed to 1’b1 prior to synthesis. See the MIV_RV32 Handbook. This user guide can be downloaded from the Libero SoC Catalog.

The following figure shows these options in the Design Flow tab.