10.2.4 Timing Analysis - Maximum Clock Frequency

The SmartTime Maximum Delay Analysis View displays the design maximum operating frequency and lists any setup violations.

- Expand Verify Post Layout Implementation.

-

Right-click Open SmartTime and choose Open

Interactively to open SmartTime.

The Maximum Delay Analysis View appears. The Maximum Delay Analysis View summarizes design performance and indicates that the design will operate at a maximum frequency of 442.48 MHz.Note: You may see a slightly different maximum frequency with a different version of Libero SoC.

Figure 10-28. Maximum Delay Analysis Summary

- Expand clk to expand the display and show the Register to Register path sets.

-

Select Register to Register to display the

register-to-register paths. Notice that the slack values are positive.

Figure 10-29. Expanded Path

-

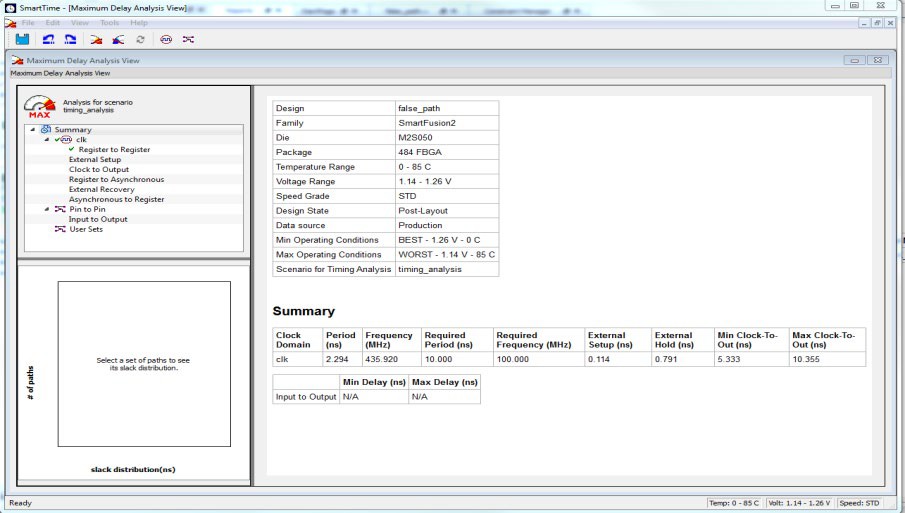

Double-click to select and expand the row in the path list with the path is

from the CLK pin of flip-flop D0_reg to the D input of flip flop Q_reg. Note

that the path goes through the S input of multiplexer un1_MUX2.

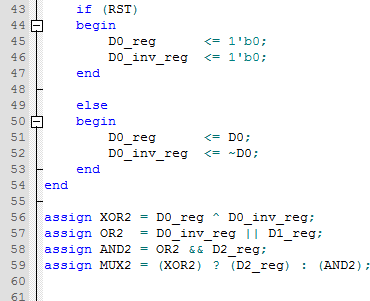

Looking at the code in false_path.v, you can see on lines 51 and 52, that D0_reg and D)_inv_reg are always the inverse of each other in "operational" mode (i.e., except for when RST is active). Line 56 says that XOR2 is the XOR of these two signals, and hence always 1 (except when RST is active). Line 59 says that XOR2 is the select of MUX2.

We might reasonably decide that we are not interested in the reset mode delay for this design; therefore, this path is a false path for our timing analysis purposes.Figure 10-30. Analyzing the False Paths

Similar analysis shows that the path from D0_inv_reg:CLK to Q_reg:D shares exactly the same false-path characteristic. We should disable both paths.

- Restart the Libero Constraints Editor. The Constraints Editor must be running to use SmartTime’s back-annotation feature. Go to the Constraint Manager tab, then go to the Timing sub-tab, pull down Edit with Constraint Editor, and choose Edit Timing Verification Constraints.

- Leave this running and return to SmartTime.

- From the Tools menu, select Max Delay Analysis.

-

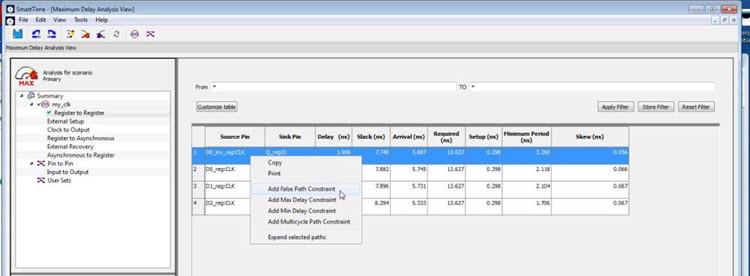

To set the path from D0_inv_reg:CLK to Q_reg :D as false, select the row

containing this path in the Register to Register path set, right-click and

choose Add False Path Constraint.

The Set False Path Constraint dialog box appears. It might pop behind the current dialog box, so check other Constraint Manager windows.

Figure 10-31. Right-clicking Add False Path Constraint

- Click OK to close the Set False Path Constraint dialog box.

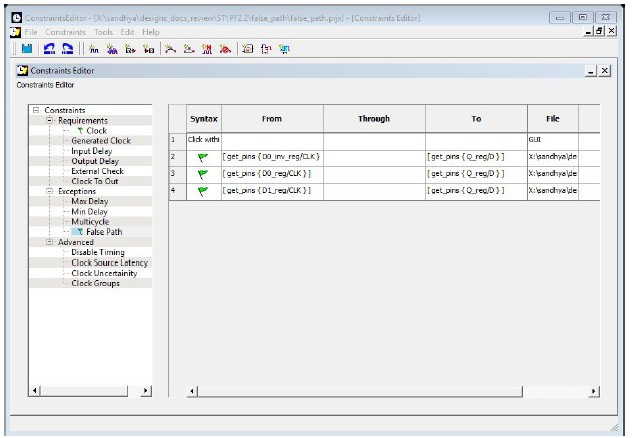

- In the Constraints Editor window, check for an entry below Exceptions > False Path.

- Return to the SmartTime window and repeat for the D0_reg:CLK -> Q_reg:D path.

- Because we are interested only in timing analysis through the MUX when select = 1, we can ignore the MUX "0" path from D1_reg:D through the AND2. We make this a false path. At this point the Constraints Editor should now look as follows. Save the file and exit the Constraints Editor and SmartTime.

-

Right-click Open SmartTime and choose Update

and Open Interactively.

You will see that Place and Route is run automatically before SmartTime is restarted.

-

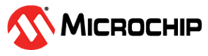

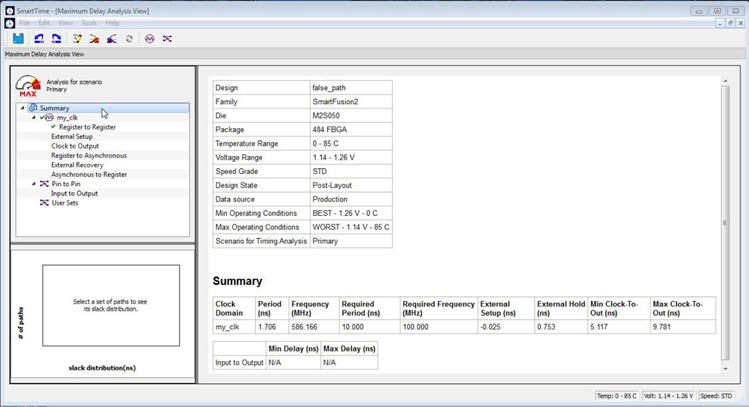

View the summary in the Maximum Delay Analysis View (Tools > Max

Delay Analysis). SmartTime now reports the maximum operating

frequency as 586.17 MHz, as shown in the following figure.

Note: The maximum operating frequency may vary slightly with a different version of the Libero software.

Figure 10-33. Maximum Delay Analysis View - Summary

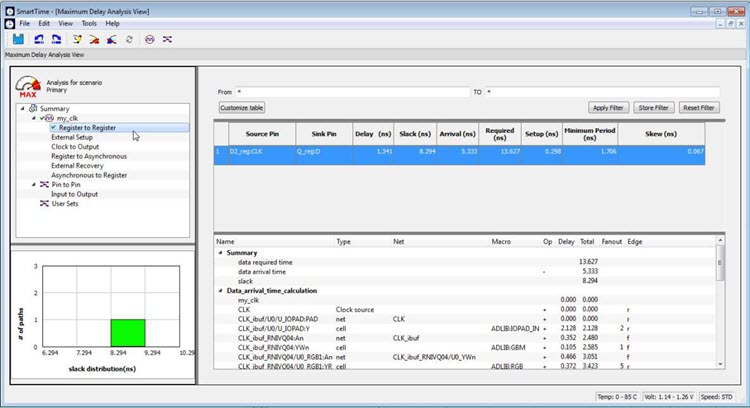

- Select the Register to Register set for my_clk. Observe that only one path is visible, from D2_reg: CLK to Q_reg:D. This is the only path that propagates a signal, as shown in the following figure.

- Close SmartTime.

- Close Libero SoC.

Place and Route is now invalidated and must be re-run before we can perform timing analysis again. This is because we changed the constraint file we are using for both P&R and for Timing Analysis. We can use different constraint files, in which case we would not need to re-run P&R.