1.2 Simulator Model

The simulator model is dependent on device architecture. The model is controlled through the MPLAB X IDE.

Architecture - 8-bit devices (AVR MCUs)

Microchip 8-bit AVR devices use Von Neumann architecture, with a single program and data memory bus.

For more information, see:

www.microchip.com/design-centers/8-bit

At the time this documentation was produced, the following ISA (instruction set architecture) cores are associated with the listed devices: ATtiny, ATmega, ATMEGAX.

Architecture - 8-bit devices (PIC MCUs)

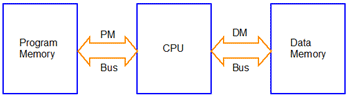

Microchip 8-bit PIC devices use Harvard architecture, with separate program and data memory buses (see figure below). Therefore, program memory instructions are not limited to data memory lengths.

Program memory, or core, instruction length is used to group 8-bit PIC MCUs. Data memory is 8-bit for these devices.

The 12-bit and 14-bit ISA core devices have word-addressed program memory space.

The 16-bit (PIC18) ISA core devices have a byte-organized program memory space. There are some restrictions in the silicon on how the program memory space can be accessed, especially when using long writes to program memory. The simulator may not show the same restrictions in all situations. Consult the data sheet for proper operation.

For more information, see:

www.microchip.com/design-centers/8-bit

At the time this documentation was produced, the following ISA (instruction set architecture) cores are associated with the listed devices:

- 12-Bit Core Device Simulation - PIC10/12/16

- 14-Bit Core Device Simulation - PIC12/16

- 16-Bit Core Device Simulation – PIC18

Architecture - 16-bit devices (dsPIC, PIC24)

Microchip 16-bit devices use a modified Harvard architecture, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces. For more information, see:

www.microchip.com/design-centers/16-bit

The dsPIC digital signal controller (DSC) is a combination of a digital signal processing (DSP) core and PIC microcontroller (MCU) peripheral features. PIC24 MCUs are basically dsPIC DSC devices without DSP capability. Both devices provide separate 24-bit program memory and 16-bit data memory spaces.

At the time this documentation was produced, the following were available devices of this type:

Architecture - 32-bit devices (PIC32M MCUs)

Microchip 32-bit PIC32M devices use MIPS® M4K® core architecture where both program and data memory are 32-bits long. For more information, see:

www.microchip.com/design-centers/32-bit

The 32-bit PIC32M core devices have a half word organized program memory space. There are some restrictions in the silicon on how the program memory space can be accessed, especially when using long writes to program memory. The simulator may not show the same restrictions in all situations. Consult the data sheet for proper operation.

At the time this documentation was produced, the following were available devices of this type:

Architecture - 32-bit devices (PIC32C/SAM MCUs)

Microchip 32-bit PIC32C/SAM devices use Arm® architecture where both program and data memory are 32-bits long. For more information, see:

www.microchip.com/design-centers/32-bit

At the time this documentation was produced, the following were available devices of this type: PIC32C, SAM.