15.13.3 SERCOM in SPI Mode in PL2

| Symbol | Parameter | Conditions | Min. | Typ. | Max. | Units | |

|---|---|---|---|---|---|---|---|

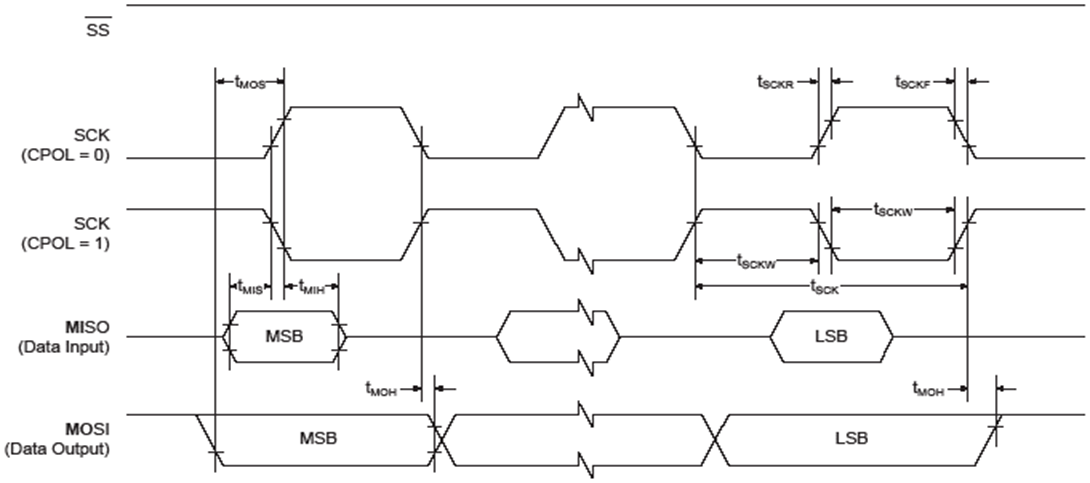

| tSCK | SCK period | Master, VDD>2.70V | 41.1 | 53 | ns | ||

| Master, VDD>1.8V | 52.6 | 65 | |||||

| tSCKW | SCK high/low width | Master | - | 0.5*tSCK | - | ||

| tSCKR | SCK rise time(2) | Master | - | 0.25*tSCK | - | ||

| tSCKF | SCK fall time(2) | Master | - | 0.25*tSCK | - | ||

| tMIS | MISO setup to SCK | Master, VDD>2.70V | 41.1 | ||||

| Master, VDD>1.8V | 52.6 | ||||||

| tMIH | MISO hold after SCK | Master, VDD>2.70V | 0 | ||||

| Master, VDD>1.8V | 0 | ||||||

| tMOS | MOSI setup SCK | Master, VDD>2.70V | 8.5 | ||||

| Master, VDD>1.8V | 13.1 | ||||||

| tMOH | MOSI hold after SCK | Master, VDD>2.70V | 0.5 | ||||

| Master, VDD>1.8V | 1 | ||||||

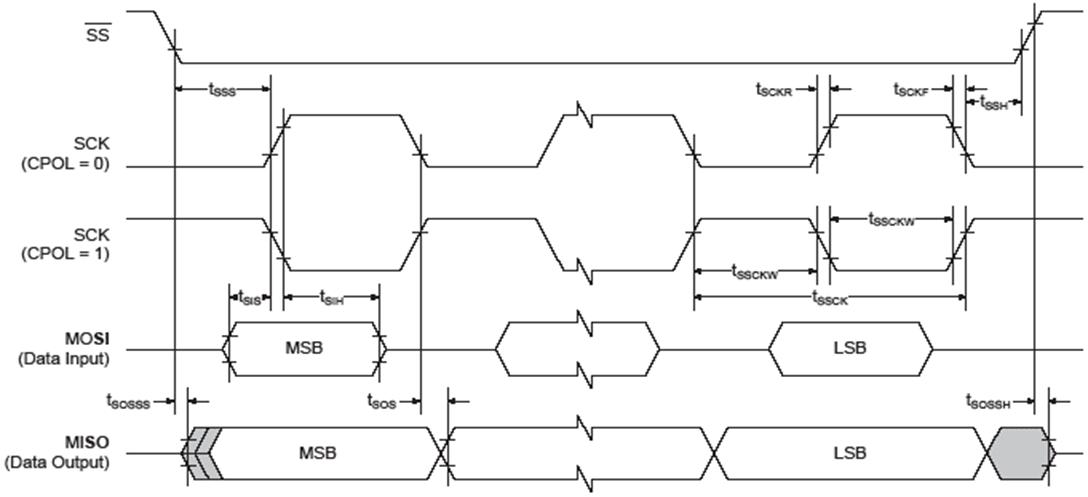

| tSSCK | Slave SCK Period | Slave, VDD>2.70V | 74 | 90 | - | ||

| Slave, VDD>1.8V | 95 | 110 | - | ||||

| tSSCKW | SCK high/low width | Slave | - | 0.5*tSCK | - | ||

| tSSCKR | SCK rise time(2) | Slave | - | 0.25*tSCK | - | ||

| tSSCKF | SCK fall time(2) | Slave | - | 0.25*tSCK | - | ||

| tSIS | MOSI setup to SCK | Slave, VDD>2.70V | 10.3 | - | - | ||

| Slave, VDD>1.8V | 11.8 | - | - | ||||

| tSIH | MOSI hold after SCK | Slave, VDD>2.70V | 0 | - | - | ||

| Slave, VDD>1.8V | 0 | - | - | ||||

| tSSS | SS setup to SCK | Slave | PRELOADEN=1 | ||||

| PRELOADEN=0 | |||||||

| tSSH | SS hold after SCK | Slave | |||||

| tSOS | MISO setup before SCK | Slave, VDD>2.70V | - | - | 36.9 | ns | |

| Slave, VDD>1.8V | - | - | 47.5 | ||||

| tSOH | MISO hold after SCK | Slave, VDD>2.70V | 11.5 | - | - | ||

| Slave, VDD>1.8V | 11.5 | - | - | ||||

| tSOSS | MISO setup after SS low | Slave, VDD>2.70V | - | - | 31 | ||

| Slave, VDD>1.8V | - | - | 41.3 | ||||

| tSOSH | MISO hold after SS high | Slave, VDD>2.70V | 6.2 | - | - | ||

| Slave, VDD>1.8V | 6.2 | - | - | ||||

Note: 1. These values are based on simulation. They are not covered

by production test limits or characterization.

Maximum SPI Frequency

- Master Mode

fSCKmax = 1/2*(tMIS + tvalid), where tvalid is the slave time response to output data after detecting an SCK edge. For a non-volatile memory with tvalid = 12ns Max, fSPCKMax = 9.8MHz @ VDDIO > 2.7V

- Slave Mode

fSCKmax = 1/2*(tSOV + tsu), where tsu is the setup time from the master before sampling data. With a perfect master (tsu=0), fSPCKMax = 16.3MHz @ VDDIO > 2.7V