3.2 SAMA5D2-PTC-EK Development Kit

The SAMA5D2-PTC-EK is a development kit built on an 8-layer PCB. The board features a SAMA5D27/BGA289 MPU and two 2-Gbit Winbond DDR2-SDRAM devices (Part No.: W972GG6KB-25).

The layout example in the above figure shows the top layer of the board focused on the DDR2-SDRAM routing. Some of the address signals and the differential clock are present on the top layer, with the mentioned trace width and minimum clearance. These values are equal to or above the minimum required. There is also a 10 mils clearance between the CK/CKn signals and any other signal, above the minimum required.

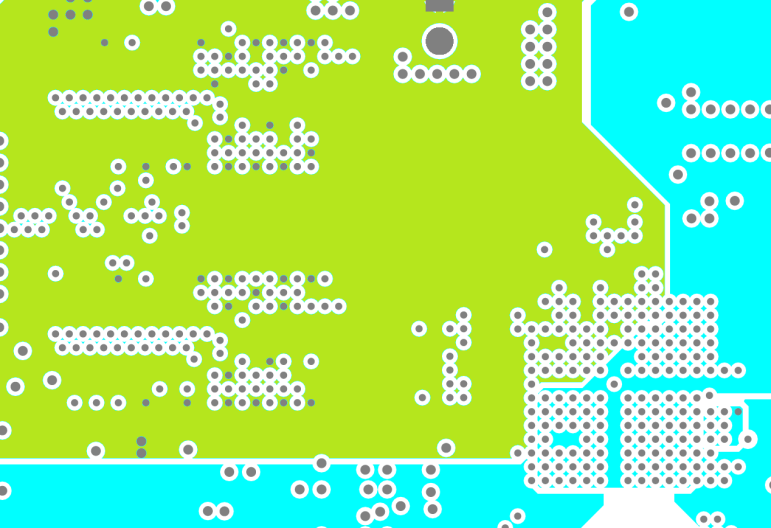

The layout example in the above figure shows the bottom layer of the DDR2-SDRAM layout. Signals from two data lanes are being routed on the bottom layer, belonging to data lane 2 (D16-D23) and data lane 0 (D0-D7), including their respective DQS/DQSn and DQM signals. Trace width used is 5 mils, and the clearance is 10 mils, both values exceeding the minimum required. On very short distances (typically the route a path needs to take to escape a dense BGA area), the clearance may go slightly below the minimum required. This is acceptable for dense designs only and shall be applied only if no other solution exists. These signals are also length-matched.

The above figure shows layer 5 of the board, used as a power plane. The highlighted region covers the traces belonging to the DDR2-SDRAM routing and serves as a reference plane for the impedance matching of the signals from layer 6 (see layer stack-up). Also, it contains no splits across any high-speed signal.

The trace impedance for inner layer 6 (see the figure below), which is used as signal layer, is calculated using the impedance formula (according to Standard IPC-2141) for an asymmetric stripline:

Equation 2

Z0(Ω)=

Where εr is the dielectric constant, H1 is the dielectric height below the signal layer, H is the dielectric height above the signal layer, W is the trace width and T the trace thickness.

In our case (available in the table SAMA5D2-PTC-EK Detailed PCB Stack-up):

- εr = 4.5 for FR-4 dielectric

- H1 = 13.8 mils below layer 6

- H = 5.12 mils above layer 6

- W = 5 mils trace width

- T = 1.38 mils copper thickness

Using the above parameters, the trace impedance is calculated to be Z0 = 48.26 Ω, covered by the ±10% tolerance.

Applying Equation 1 for traces on the top or bottom layer, for the above parameters and a dielectric height H = 3.63 mils, results in a near perfect 49.92 Ω trace impedance.

| Layer Name | Type | Material | Thickness [mm] | Thickness [mil] | Dielectric Material | Dielectric Constant |

|---|---|---|---|---|---|---|

| Top Overlay | Overlay | – | – | – | – | – |

| Top Solder | Solder Mask/Coverlay | Surface Material | 0.01016 | 0.4 | Solder Resist | 3.5 |

| TOP | Signal | Copper | 0.035052 | 1.38 | – | – |

| Dielectric1 | Dielectric | Core | 0.092202 | 3.63 | FR-4 | 4.5 |

| GND02 | Signal | Copper | 0.035052 | 1.38 | – | – |

| Dielectric2 | Dielectric | Core | 0.130048 | 5.12 | FR-4 | 4.5 |

| ART03 | Signal | Copper | 0.035052 | 1.38 | – | – |

| Dielectric3 | Dielectric | Core | 0.35052 | 13.8 | FR-4 | 4.5 |

| PWR04 | Signal | Copper | 0.035052 | 1.38 | – | – |

| Dielectric4 | Dielectric | Core | 0.130048 | 5.12 | FR-4 | 4.5 |

| PWR05 | Signal | Copper | 0.035052 | 1.38 | – | – |

| Dielectric5 | Dielectric | Core | 0.35052 | 13.8 | FR-4 | 4.5 |

| ART06 | Signal | Copper | 0.035052 | 1.38 | – | – |

| Dielectric6 | Dielectric | Core | 0.130048 | 5.12 | FR-4 | 4.5 |

| GND07 | Signal | Copper | 0.035052 | 1.38 | – | – |

| Dielectric7 | Dielectric | Core | 0.092202 | 3.63 | FR-4 | 4.5 |

| BOTTOM | Signal | Copper | 0.035052 | 1.38 | – | – |

| Bottom Solder | Solder Mask/Coverlay | Surface Material | 0.01016 | 0.4 | Solder Resist | 3.5 |

| Bottom Overlay | Overlay | – | – | – | – | – |