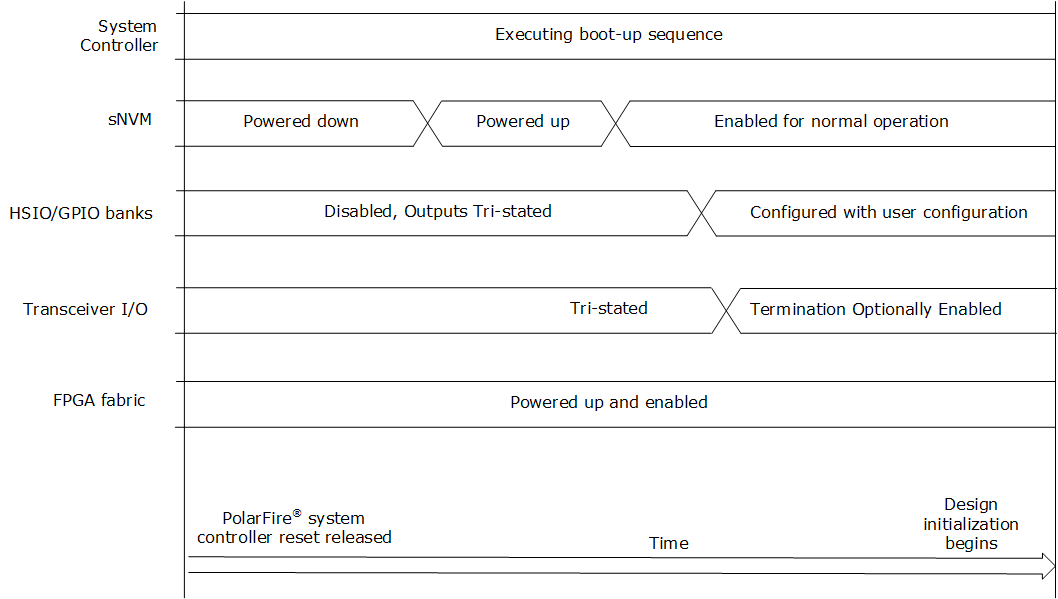

2.2 Device Boot

(Ask a Question)After POR circuitry releases the System Controller from reset, the device boot-up procedure is executed by the System Controller to bring up the FPGA fabric and related I/Os. The System Controller always executes the same device boot-up sequence irrespective of the user design.

The following events occur during device boot-up:

- sNVM is powered up and enabled for normal operation.

- Transceiver I/Os are enabled.

- User voltage detectors are enabled.

- FPGA fabric is powered up and enabled.

- HSIO and GPIO banks are configured based on the user configuration in the Libero® SoC.

- I/Os are operational at this time but may not meet performance specifications until the calibration completes.

- MSS is powered down and MSSIOs are tristated (for PolarFire SoC and RT PolarFire SoC FPGA only).

The following illustration shows the boot-up sequence for a programmed PolarFire FPGA device.