2.8 Managing Global Signals

(Ask a Question)Assigning high fan-out nets, such as clocks and resets, to the global clock network is an effective way to reduce routing congestion and minimize skew. Due to its high propagation delays, the global clock network is not recommended for use in timing-critical data paths.

The clock macros can be used for assigning signals to the global clock network:

- The CLKBUF macro connects a preferred clock input to a GB. Preferred clock inputs have direct hardwired routing to GBs.

- The CLKINT macro connects a fabric-routed signal to a GB. The CLKINT macro must be used to connect a regular I/O to GB through the FPGA fabric.

- The RCLKINT macro connects a fabric-routed signal to RGB.

The CCCs, on-chip oscillators, clock dividers, NGMUXs, and transceivers drive GBs through hardwired routing.

Libero SoC supports automated global buffer allocation to minimize user intervention. The allocation strategy for global buffers employs the following priority:

- User-inserted global clock macros

- Clock nets

- Asynchronous reset/set nets

- Very high fan-out nets

In the Libero SoC, the default fan-out threshold for global net promotion is larger for data pins (pins involved in register-to-register paths) than asynchronous logic pins (pins involved in register-to-asynchronous paths).

Due to this, the automated design flow is more likely to employ global nets on register-to-asynchronous paths than register-to-register paths. The reasoning for this is that asynchronous pins are not normally timing-critical, and routing them on global nets reduces routing congestion. However, register-to-asynchronous paths are functionally equivalent to register-to-register paths from the perspective of achieving timing closure. As a result, when designing register-to-asynchronous paths, ensure that timing-critical connections do not unnecessarily employ global nets.

If a design contains a failing register-to-asynchronous timing path, check if the path drives a global net in SmartTime. This is done by examining the path and looking for a GB between its launching and latching registers. If a GB is present, you may be able to improve the likelihood of timing closure by demoting the net to a fabric-routed net. An asynchronous net can be demoted by increasing the fan-out threshold of asynchronous pins above the fan-out of the asynchronous net. Alternatively, you can manually adjust the RTL by moving timing-critical pins from high-fan-out asynchronous nets to lower fan-out nets.

Users have the option of setting the minimum fan-out for automatic global assignment. The fan-out threshold values are set in the Libero SoC to automate clock pin promotion to global nets.

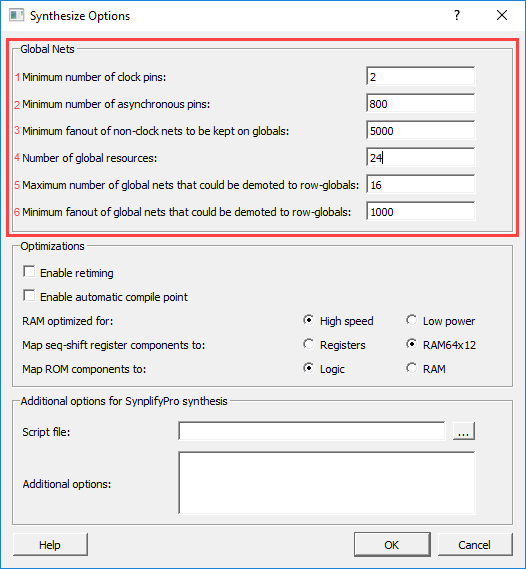

In the Libero Design Flow window, expand Implement Design, right-click Synthesize, and choose Configure Options. This opens the Synthesize Options dialog box, as shown in the following figure.

The following options specify the fan-out threshold value for net promotion and demotion:

- Minimum number of clock pins: Specifies the fan-out threshold value for clock pin promotion. The default value is 2.

- Minimum number of asynchronous pins: Specifies the fan-out threshold value for asynchronous pin promotion. The default value is 800.

- Minimum fan-out of non-clock nets to be kept on globals: Specifies the fan-out threshold value for data pin promotion to global resources. It is the minimum fan-out of non-clock (data) nets to be kept on global nets (no demotion). The default value is 5,000 (must be between 1,000 and 200,000). If you run out of global resources for your design, increase this number. If a CLKINT net with fan-out less than this threshold value has data pins along with some clock or asynchronous reset/set pin, move all the data pins to the CLKINT driver net.

- Number of global resources: Specifies the number of global resources to be used in the design. The default value is 24 and you can increase its value up to 48.

- Maximum number of global nets that could be demoted to row-globals: Specifies the maximum number of global nets that could be demoted to RGB resources. The default value is 16 (must be between 0 and 50).

- Minimum fan-out of global nets that could be demoted to row-globals: Specifies the minimum fan-out of global nets that could be demoted to RGB resources. The default value is 1,000 (must be between 25 and 5,000). It is undesirable to have high fan-out clock nets demoted using RGB resources because it may result in high skew. If you run out of global resources for your design, reduce this number to allow more globals to be demoted to RGB resources.

After synthesis, the compiler tool performs the following steps to assign nets to global buffers:

- Sorting all CLKINT nets in the following priority order:

- Fan-out, only if fan-out ≥ threshold value specified by minimum fan-out of non-clock nets to be kept on globals

- Number of clock pins

- Number of asynchronous reset/set pins

- Number of data pins

- Determining the number of GB resources available for CLKINT nets after allocating them to any of the CLKBUF, CLKINT_PRESERVE, and GCLKINT nets.

- Demoting CLKINT nets from the sorted list that are beyond the limit specified by the number of global resources.

- If such a net has at least the number of pins specified by minimum fan-out of global nets that could be demoted to row-globals, replace the CLKINT with an RCLKINT macro. Limit the number of nets demoted to RCLKINT to the count specified by maximum number of global nets that could be demoted to row-globals.

- Otherwise, merge the net with the driver of the CLKINT.

The HDL source file or SmartDesign schematic is the preferred place for defining which signals must be assigned to the global network using clock macro instantiation. A signal with high-fan-out may have logic replication if it is not promoted to a global during synthesis.