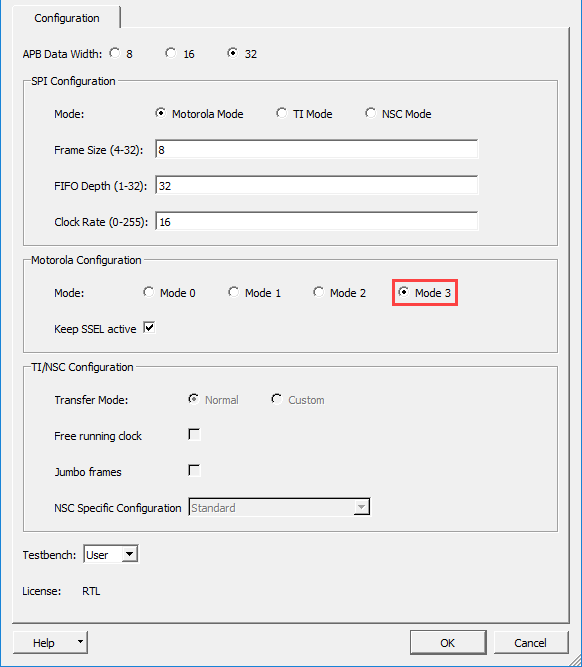

1.4.1.4 CoreSPI Configuration

(Ask a Question)The CoreSPI is used to program the external SPI Flash using Mi-V processor. PF_SPI macro interfaces the fabric logic to the external SPI Flash, which is connected to System Controller.

- APB Data Width: Select 32 as APB data width in the design. The default value is 8.

- Mode: Select Motorola Mode (default) as the target SPI target supports Motorola mode. Mode 3 is selected under Motorola Configuration.

- Frame Size: Enter 8. The default value is 4.

- FIFO Depth: Enter 32 to store maximum frames (Tx and Rx) in FIFO. The default value is 4.

- Clock Rate: Enter 16. The default value is 8. The SPI clock becomes system clock/ 2*(16+1).

- Keep SSEL active: Enabled to keep the target peripheral active between back-to-back data transfers.

The following figure shows the CoreSPI configurator.