20.2.2.3.1 Clocks

(Ask a Question)Use the Clocks tab to configure the MSS PLL clock frequency and clock sources. For more information, see the PolarFire Family Clocking Resources User Guide .

- MSS PLL

- DDR PLL

- SGMII PLL

Each PLL generates four output clocks from one input reference clock.

The actual output that PLL Solver generates is shown in the GUI next to the Actual: label. If the requirement is met, the color of the label is blue. If it is not met (from you), it is red.

- Output 0 (CPU Clock)

- Output 1 (Crypto Clock)

- Output 2 (eMMC Clock)

- Output 3 (CAN Clock)

The following conditions pose restrictions on the PLL solver. Solver attempts to solve the fixed requirements first and then the ones without restriction.

- When eMMC is enabled, the output clock requirement is fixed at 200 MHz.

- When the CAN peripheral is enabled, the output clock requirement must be a multiple of 8 (maximum 80 MHz).

- Crypto can be at most 200 MHz for STD speed grade and 213 MHz for -1 speed grade.

- CPU has the maximum frequency of 625 MHz for STD

speed grade and 667 MHz for -1 speed grade.Note: When the actual frequency found by the PLL solver exceeds the maximum required clock frequency for MSS PLL and Crypto, MSS generation fails with the following error message.

ERROR: Invalid solution found for Output0 of MSS PLL. 800 MHz is greater than the supported value of 667 MHz.

In DDR PLL, enter the required output clock frequency in the DDR tab in Line Edit "Memory clock frequency." All four output clocks are generated by the PLL that has the same frequency.

In SGMII PLL, the output frequency requirement is fixed at 625 MHz for all four outputs. You do not have to enter this. Additionally, the output clocks are phase-shifted by 90° (output clock 0 has a 0° phase shift, output clock 1 has a 90° phase shift, and so on).

| Option | Description |

|---|---|

| eMMC/SD/SDIO clock source |

eMMC/SD/SDIO can be clocked either through MSS PLL or Fabric I/O. |

| CAN clock source | CAN can be clocked either through MSS PLL or Fabric I/O. |

| MSS PLL reference clock source | MSS can be clocked from dedicated I/O from Bank 5 (REFCLK) or North West PLL output. |

| MSS PLL required clock frequency |

|

| MSS CPU cores clock frequency divider | The MSS CPU clock frequency is based on the MSS PLL clock frequency and is set using the divider values /1, /2, /4, or /8. The frequency must be greater than or equal to the MSS AXI clock, and can have a maximum value of 667 MHz for -1 speed, and 625 MHz for STD speed. |

| MSS AXI clock frequency divider | The MSS AXI clock frequency is based on the MSS CPU clock frequency and is set using the divider values of /1, /2, /4, or /8. The frequency must be greater than or equal to MSS AHB/APB clock, and can have a maximum value of 333.50 MHz for -1 speed, and 312.50 MHz for STD speed. |

| MSS AHB/APB clock frequency divider | The MSS AHB/APB clock frequency is based on the MSS CPU clock frequency and is set using the divider values /2, /4, or /8. The maximum supported frequency is 166.75 MHz for -1 speed, and 156.25 MHz for STD speed. |

| DDR reference clock source | You can select the North West (NW) PLL ports or I/Os from Bank 5. |

| RTC/MAC SGMII reference clock input source | You can select the NW PLL ports or I/Os from Bank 5. |

| Dedicated I/O from Bank5 (REFCLK) frequency | This is a dedicated I/O from Bank 5 to the MSS PLL. It can either be 100 MHz or 125 MHz. |

| NW PLL (REF_0_PLL_NW) frequency (MHz)/NW PLL (REF_1_PLL_NW) frequency (MHz) | This option is available when any peripheral is clocked from NW PLL output. It can be any value between 50 MHz and 125 MHz. |

| Crypto clock frequency from MSS (MHz) | You can set the reference clock frequency for Crypto between 1 MHz and 200 MHz for STD speed grade, and between 1 MHz and 213 MHz for -1 speed grade. |

| MSS CAN clock frequency (MHz) | The MSS CPU clock frequency is based on the MSS PLL clock frequency. The supported frequencies in MHz are 8, 16, 24, 32, 40, 48, 56, 64, 72, and 80. |

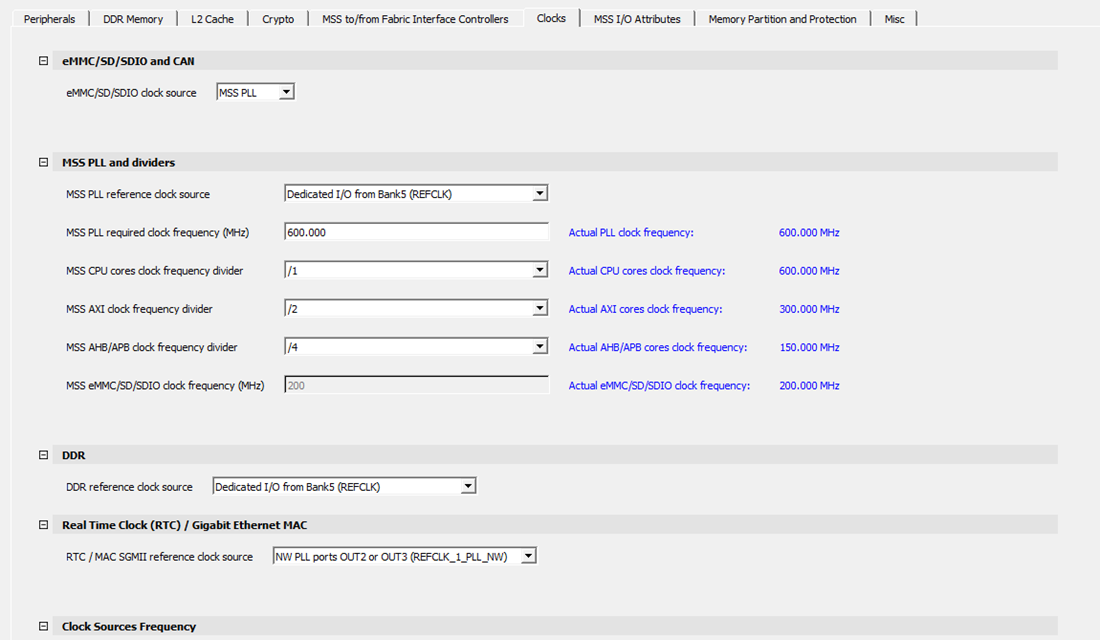

The following figure shows the Clocks tab in the PolarFire SoC MSS Configurator. In this example, the following configurations are used:

- Dedicated I/Os from Bank 5 (REFCLK) are selected as the reference clock input source for the MSS. The MSS PLL clock frequency is set to 600 MHz.

- Dedicated I/Os from Bank 5 (REFCLK) are used to source the reference clock input frequency for the DDR subsystem.

- The DDR clock source and MSS clock source are set to 125 MHz.

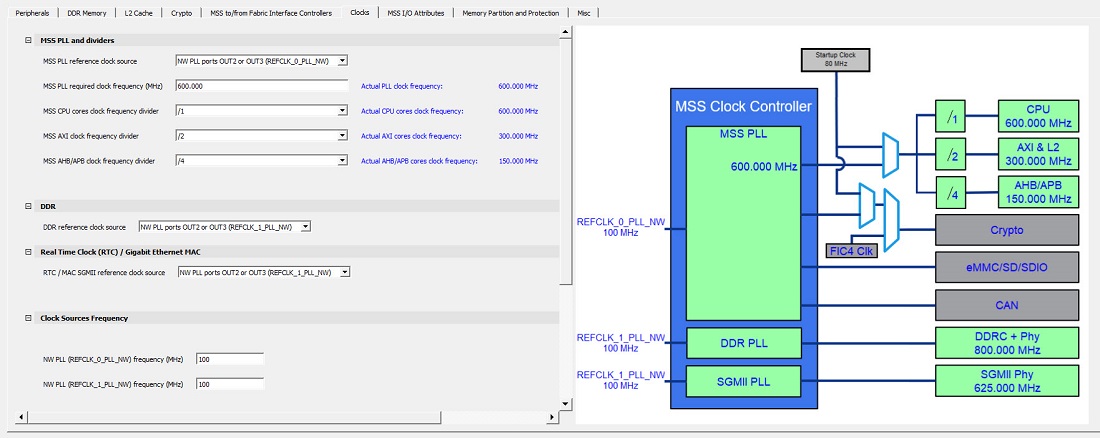

The following figure shows the Clocks tab with PLL in the PolarFire SoC MSS Configurator. In this example, the following configuration is used:

- NW PLL ports OUT2 or OUT3 (REFCLK_0_PLL_NW) are selected as the reference clock input source for the MSS. The MSS PLL clock frequency is set to 600.000 MHz.

- NW PLL ports OUT2 or OUT3 (REFCLK_1_PLL_NW) are used to source the reference clock input frequency for the DDR subsystem and Real Time Clock/Gigabit Ethernet MAC.

- The DDR Clock Source and MSS Clock Source are set to 100 MHz.