Aggregate Memory Type (array, struct, or class)

(Ask a Question)When the memory has more than 1 elements (not a scalar type memory), SmartHLS™ creates an interface with two RAM ports. Each RAM port can do both read and write to the external RAM. A one cycle read latency is expected. Typically an external true dual-port RAM can be connected to the interface, allowing both ports to perform independent reads/writes simultaneously. The same port will not perform read and write at the same cycle. Simultaneous writes from both ports are ensured to be with different write addresses.

The table below lists the signals of each RAM port, with "_a" and "_b" suffixes respectively. Some signals are not available when the memory is read-only or write-only, i.e., when the top-level function (and its descendant functions) never write to or read from the memory.

| Port Name | Direction | Description |

|---|---|---|

| <ARG_NAME>_address_<a|b> | OUT | The address pointing to the RAM entry that SmartHLS module wants to access. |

| <ARG_NAME>_read_en_<a|b> | OUT | Read enable port (n/a for write-only memory). |

| <ARG_NAME>_read_data_<a|b> | IN | Read data port (n/a for write-only memory). |

| <ARG_NAME>_write_en_<a|b> | OUT | Write enable port (n/a for read-only memory). |

| <ARG_NAME>_byte_en_<a|b> | OUT | Byte-enable port. Only available if the memory requires writes to partial bytes of a memory word. (n/a for read-only memory, or when all write operations update the whole memory words). |

| <ARG_NAME>_write_data_<a|b> | OUT | Write data port (n/a for read-only memory). |

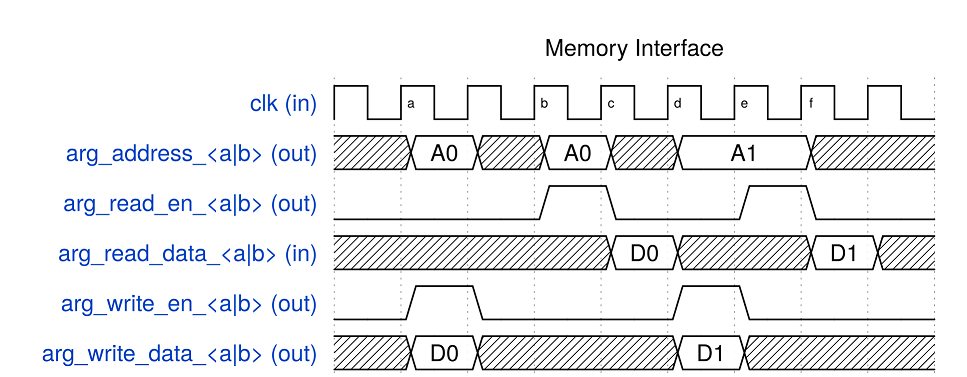

- At Cycle a, the top-level module performs a write operation to the connected external memory, by setting thearg_write_en port to high and providing the address "A0" and write data "D0" on the arg_address andarg_write_data ports respectively.

- At Cycle b, the top-level module issues a read from the connected external memory by setting arg_address to the read address "A0" and arg_read_en to high. SmartHLS module expects the read data "D0" to be available on thearg_read_data port in the subsequent cycle (i.e., Cycle c).

- At Cycle d, the top-level module writes "D1" to address "A1"

- Keeping the address port the same and setting arg_read_en high at the next cycle, the top-level module reads from address "A1" at Cycle e, and expects to receive "D1" at the right next cycle at Cycle f.