5.13 References

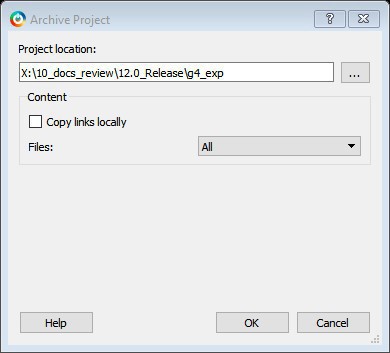

(Ask a Question)5.13.1 Archive Project Dialog Box

(Ask a Question)The Archive Project dialog box enables you to create an archive (*.zip file) of

your existing project and save it at the specified location. This is useful if you want

to create a quick zip file of your project. Archive Project and

Save As Project are functionally equivalent; however, if you

are saving your Libero application to the SVN repository, it is important to archive

your project. When you do an SVN checkout after checkin, timestamps might be outdated,

and the tool states will remain invalidated. Archive Project helps in retaining the tool

states by preserving the database in compressed format.

To access this dialog box, choose Archive Project from the Project menu.

Project Location. Accept the default location or browse to a new location

where you want to save the archive (*.zip) file. The *.zip file is

named <project_name>.zip.

Copy links locally. Check this check box to copy the links from your current project into your archive. Otherwise, the links will not be copied and you must add them manually.

Files. Specifies the kind of files that are archived.

- All. Includes in the archive all your project and source files; the state of the project is retained.

- Project files only: Includes in the archive only the project-related information required to retain the state of the project.

- Source files only: Includes in the archive only the source files. This means the configuration of all the tools in the toolchain is retained but the states are not. Source files means constraint information and component information available in the component, hdl and smartgen directories.

Files are archived for different selections as shown in the following table.

| Folder Name | Files | ||

|---|---|---|---|

| All | Project Files Only | Source Files Only | |

component | All Files | All Files | All Files |

constraint | All Files | All Files | All Files |

hdl | All Files | All Files | All Files |

stimulus | All Files | All Files | All Files |

viewdraw | All Files | All Files | All Files |

smartgen | All Files | All Files | All Files |

|

firmware |

All Files |

All Files |

All Files |

|

CoreConsole |

All Files |

All Files |

All Files |

|

SoftConsole/Keil/IAR |

All Files |

All Files |

All Files |

|

simulation |

All Files |

*.ini, *.bfm, *.do., *.vec |

*.ini, *.bfm, *.do., *.vec |

|

synthesis |

All Files |

*.edn, *.vm, *.sdc, *.so, *.prj, *.srr, *.v, run_options.txt, synplify.log |

*.prj files |

|

Designer/impl1 |

All Files |

All Files |

*.ide_des files |

|

Designer/<root> |

All Files |

All Files |

Not archived |

|

tooldata |

All Files |

All Files |

All Files |

5.13.2 Adding or Modifying Bus Interfaces in SmartDesign

(Ask a Question)SmartDesign supports automatic creation of data driven configurators based on HDL generics/parameters. You can add a bus interface from your HDL module, or you can add it from the Catalog.

To add a bus interface using your custom HDL block:

If your block has all the necessary signals to interface with the AMBA bus protocol (such as address, data, and control signals):

- Right-click your custom HDL block and choose Create Core from HDL. The Libero SoC creates your core and asks if you want to add bus interfaces.

- Click Yes to open the Edit Core Definition dialog box and add bus interfaces. Add the bus interfaces, as necessary.

- Click OK to continue.

Now your instance has a proper AMBA bus interface on it. You can manually connect it to the bus or let Auto Connect find a compatible connection.

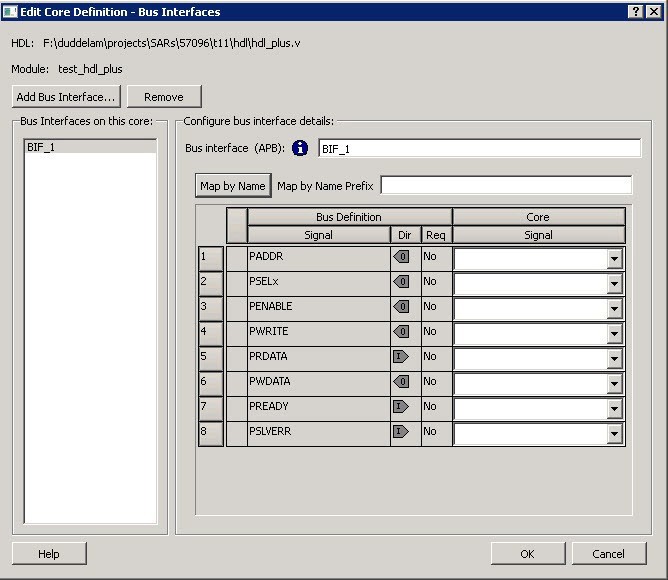

To add (or modify) a bus interface to your Component:

- Right-click your Component and choose

Edit Core Definition. The Edit Core Definition dialog box opens, as shown

in the following figure.

Figure 5-237. Edit Core Definition Dialog Box

- Click Add Bus Interface. Select the bus interface you want to add and click OK.

- If necessary, edit the bus interface details.

- Click Map by Name to map the signals automatically. Map By Name attempts to map any similar signal names between the bus definition and pin names on the instance. During mapping, bus definition signal names are prefixed with text entered in the Map by Name Prefix field.

- Click OK to continue.

- Bus Interface: Name of bus interface. It can be edited as required. Bus Definition: Specifies the name of the bus interface. Role: Identifies the bus role (master or slave).

- Vendor: Identifies the vendor for the bus interface.

- Version: Identifies the version for the bus interface.

Configuration Parameters

- Parameter: Specifies the parameter name.

- Value: Specifies the value you define for the parameter.

- Consistent: Specifies whether a compatible bus interface must have the same value for this bus parameter. If the bus interface has a different value for any parameters that are marked with consistent set to yes, this bus interface will not be connectable.

Signal Map Definition

The signal map of the bus interface specifies the pins on the instance that correspond to the bus definition signals. The bus definition signals are shown on the left, under the Bus Interface Definition. This information includes the name, direction and required properties of the signal.

The pins for your instance are shown in the columns under the Component Instance. The signal element is a drop-down list of the pins that can be mapped for that definition signal.

If the Req field of the signal definition is Yes, you must map it to a pin on your instance for this bus interface to be considered legal. If it is No, you can leave it unmapped.

5.13.2.1 Bus Interfaces

(Ask a Question)When you add a bus interface, the Edit Core Definition dialog box provides the following Microchip Libero SoC-specific bus interfaces:

- AHB – Master, Slave, MirroredMaster, MirroredSlave

- APB – Master, Slave, MirroredMaster, MirroredSlave

- AXI – Master, Slave, MirroredMaster, MirrorSlave, System

- AXI 4 – Master, Slave, MirroredMaster, MirrorSlave

5.13.3 Catalog

(Ask a Question)In the Libero SoC, from the View menu choose Windows > Catalog.

The Catalog displays a list of available cores, buses, and macros.

From the Catalog, you can create a component from the list of available cores, add a processor or peripheral, add a bus interface to your SmartDesign component, instantiate simulation cores or add a macro (Arithmetic, Basic Block, and so on.) to your SmartDesign component.

- Double-click a core to configure it and add it to your design. Configured cores are added to your list of Components/Modules in the Design Explorer.

- Check the Simulation Mode check box to instantiate simulation cores in your SmartDesign Testbench. Simulation cores are basic cores that are useful for stimulus, such as driving clocks, resets, and pulses.

Viewing Cores in the Catalog

The font indicates the status of the core:

- Plaintext - In vault and available for use

- Asterisk after name (*) - Newer version of the core (VLN) available for download

- Italics - Core is available for download but not in your vault

- Strikethrough - core is not valid for this version of Libero SoC

The colored icons indicate the license status. Blank means that the core is not license protected in any way. Colored icons mean that the core is license protected, with the following descriptions.

Green Key - Fully licensed; supports the entire design flow.

Yellow Key - Has a limited or evaluation license only. Precompiled simulation libraries are provided, enabling the core to be instantiated and simulated within Libero SoC. Using the Evaluation version of the core it is possible to create and simulate the complete design in which the core is being included. The design is not synthesizable (RTL code is not provided). No license feature in the license.dat file is needed to run the core in evaluation mode. You can purchase a license to generate an obfuscated or RTL netlist.

Yellow Key with Red Circle - License is protected. You are not licensed to use this core.

- Right-click any item in the Catalog and choose Show Details for a short summary of the core specifications.

- Choose Open Documentation for more information on the Core.

- Right-click and choose Configure Core to open the core generator.

- Click the Name column heading to sort the cores alphabetically.

- Filter the cores according to the data in the Name and Description fields.

- Type the data into the filter field to view the cores that match the filter.

- Set the Display setting in the Catalog Options to List cores alphabetically while using the filters to search for cores. By default, the filter contains a beginning and ending ‘*’, so if you type ‘controller’ you get all cores with controller in the core name (case insensitive search) or in the core description. For example, to list all the Accumulator cores, in the filter field type:

accu

Catalog Options

Click the UI control button

Import a core from a file when:

- You do not have access to the internet and cannot download the core, or

- A core is not completed and not posted to the web (you have an evaluation core)

Manually Downloading MegaVaults and Individual CPZ files

When Libero is used in an environment without automatic access to Microchip's online IP repositories via the Internet; see this article explaining how to download MegaVaults and individual CPZ files.

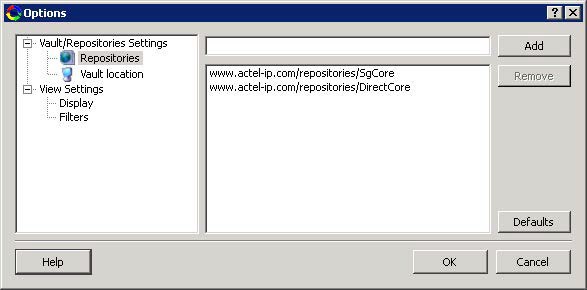

5.13.3.1 Catalog Options Dialog Box

(Ask a Question)The following Catalog Options dialog box allows you to customize your Catalog. You can add a repository, set the location of your vault, and change the View Settings for the Catalog. To display this dialog box, click the Catalog Options button

- Vault/Repositories Settings

- Repositories:

A repository is a location on the web that contains cores that can be included in your design.

The Catalog Options dialog box enables you to specify which repositories you want to display in your Vault. The Vault displays a list of cores from all your repositories, and the Catalog displays all the cores in your Vault.

The default repository cannot be permanently deleted; it is restored each time you open the Manage Repositories dialog box.

Any cores stored in the repository are listed by name in your Vault and Catalog; repository cores displayed in your Catalog can be filtered like any other core.

Type in the address and click the Add button to add new repositories. Click the Remove button to remove a repository (and its contents) from your Vault and Catalog. Removing a repository from the list removes the repository contents from your Vault.

- Vault location

Use this option to choose a new vault location on your local network. Enter the full domain pathname in the Select new vault location field. Use the format:

\\server\share

and the cores in your Vault will be listed in the Catalog.

Set ENV variable to set vault location - In addition to setting the vault location using the Catalog dialog box, you can set the vault location using the environment variable MSCC_IDE_VAULT_LOCATION. Setting the vault through the environment variable takes precedence over all other options to set vault location.

To set the vault location on Linux, type the following command:

setenv MSCC_IDE_VAULT_LOCATION /home/temp_dir

To set the vault location on Windows:

Add a new environment variable MSCC_IDE_VAULT_LOCATION in System Properties and specify your vault location.

- Read only

vault

In read only Mega Vault mode, you cannot download, add, or remove cores. However, you can configure and generate cores by creating a temporary extract location to extract the core. This temporary extract location can be set by setting the environment variable MSCC_IDE_VAULT_EXTRACT_LOCATION. By setting this environment variable, your configured cores are retained across sessions.

To set the extract location on Linux, type the following command:

setenv MSCC_IDE_VAULT_EXTRACT_LOCATION /home/vault_extract

To set the extract vault location on Windows:

- Add a new environment variable MSCC_IDE_VAULT_EXTRACT_LOCATION in System Properties and specify your extract location.

- If you do not specify the extract location, a temporary location will be created by Libero and it will be accessed only while the current session is active. If the session is no longer active, the temporary extract location will be cleaned up by Libero. If you specify the extract location, it will be available for any instance of Libero on that machine, and it is your responsibility to clean up the extract location.

- Repositories:

- View Settings

- Display

Group cores by function - Displays a list of cores, sorted by function. Click any function to expand the list and view specific cores.

List cores alphabetically - Displays an expanded list of all cores, sorted alphabetically. Double-click a core to configure it. This view is often the best option if you are using the filters to customize your display.

Show core version - Shows/hides the core version.

- Filters

Filter field - Type text in the Filter Field to display only cores that match the text in your filter. For example, to view cores that include 'sub' in the name, set the Filter Field to Name and type sub.

Display only latest version of a core - Shows/hides older versions of cores; this feature is useful if you are designing with an older family and wish to use an older core.

Show all local and remote cores - Displays all cores in your Catalog.

Show local cores only - Displays only the cores in your local vault in your Catalog; omits any remote cores.

Show remote cores that are not in my vault - Displays remote cores that have not been added to your vault in your Catalog.

- Display

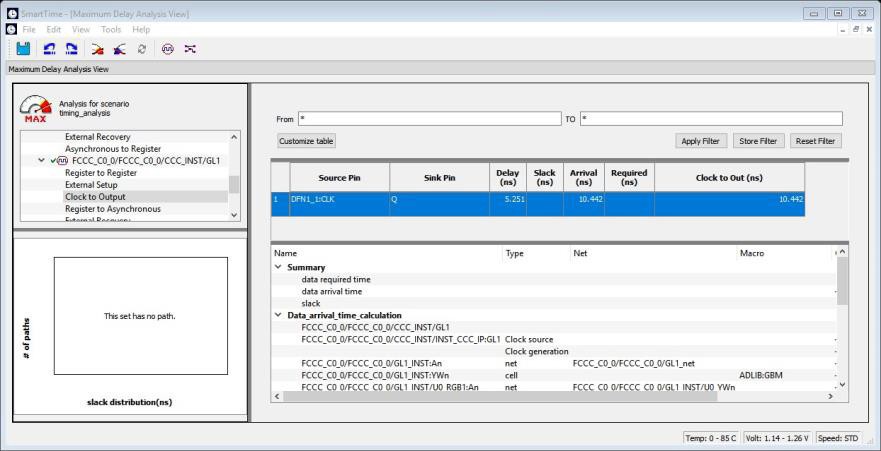

5.13.4 Changing Output Port Capacitance

(Ask a Question)Output propagation delay is affected by both the capacitive loading on the board and the I/O standard. The I/O Attribute Editor in Chip Planner provides a mechanism for setting the expected capacitance to improve the propagation delay model. SmartTime automatically uses the modified delay model for delay calculations.

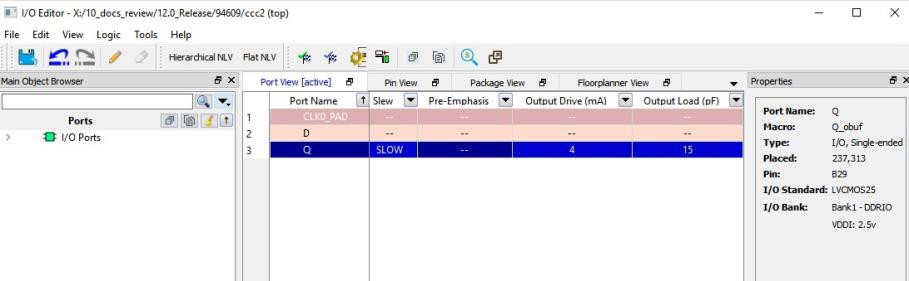

To change the output port capacitance and view the effect of this change in SmartTime Timing Analyzer, refer to the following example. The following figure shows the delay from DFN1 to output port Q. It shows a delay of 6.603 ns based on the default loading of 5 pF.

If your board has output capacitance of 15 pf on Q, you must perform the following steps to update the timing number:

- Open the I/O Attribute Editor and change the output load to 15 pf.

Figure 5-241. I/O Attribute Editor View

- Select File > Save.

- Select File > Close.

- Open the SmartTime Timing Analyzer.

You can see that the Clock to Output delay changed to 5.952 ns.

5.13.5 Core Manager

(Ask a Question)The Core Manager only lists cores that are in your current project. If any of the cores in your current project are not in your vault, you can use the Core Manager to download them all at once.

For example, if you download a sample project and open it, you might not have all the cores in your local vault. In this instance you can use the Core Manager to view and download them with one click. Click Download All to add any missing cores to your vault. To add any individual core, click the green download button.

| Column | Description |

|---|---|

| Name | Name of the core. |

| Vendor | Source of the core. |

| Core Type | Core type. |

| Version | Version of the core used in your project. If the version is a later version than the one in your vault, click Download All to download the latest version. |

5.13.6 Configure Security Locks for Production

(Ask a Question)Configure Security Locks for Production is a GUI-based tool that guides the user on how to configure the Permanent Locks for Production. The wizard has six steps/pages executed in sequential order. One Time Programmable (OTP) settings in the Permanent Locks page are applied to configured Security settings from the Configure Security tool. The subsequent pages have read only fields, which will be affected by Permanent Lock settings. These settings can only be configured by the Configure Security tool.

If you configure any Permanent Lock settings, you will be forced to go through each page to review the Security settings to make sure they are as desired. The settings cannot be changed once they are programmed.

- Permanent Locks and One-way Passcode

- User keys in Configure Security

- Update Policy in Configure Security

- Debug Policy in Configure Security

- Microsemi Factory Access in Configure Security

- JTAG/SPI Slave Commands Policy in Configure Security

Summary Window

The summary window displays the summary of the current page configuration settings. Based on the selection made in the first page, the summary for the subsequent pages change. The window will scroll to the current page as you move from page to page.

Back

Click Back to return to the previous step.

Next

Click Next to proceed to the next step.

Finish

Click Finish to complete the configuration after executing the all the steps in sequential order.

Save Summary to File

Click Save Summary to File to save the display in the Summary field to a file.

5.13.7 Importing Source Files by Copying Files Locally

(Ask a Question)Designer in Libero SoC cannot import files from outside your project without copying them to your local project folder. You might import source files from other locations, but they are always copied to your local folder. Designer in Libero SoC always audits the local file after you import; it does not audit the original file.

When the Project Manager asks you if you want to copy files "locally", it means 'copy the files to your local project folder'. If you do not wish to copy the files to your local project folder, you cannot import them. Your local project folder contains files related to your Libero SoC project.

Files copied to your local folders are copied directly into their relevant directories: netlists are copied to the synthesis folder; source files are copied to hdl folder, constraint files to constraint folder, and so on. The files are also added to the Libero SoC project and appear in the Files tab.

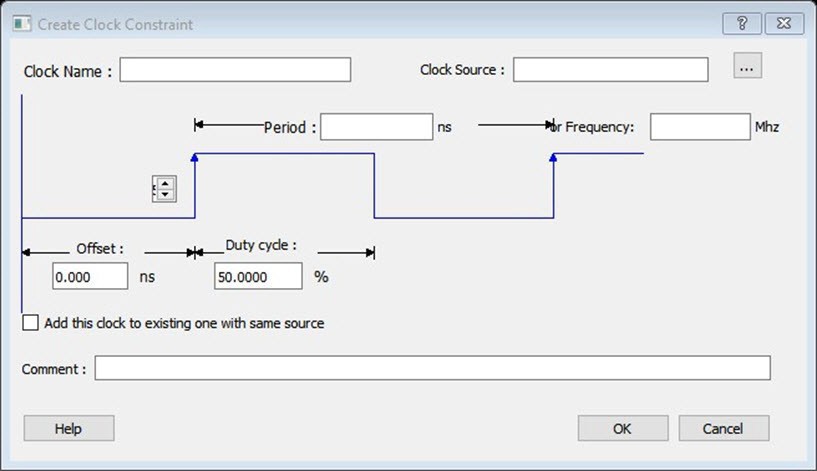

5.13.8 Create Clock Constraint Dialog Box

(Ask a Question)Use this dialog box to enter a clock constraint setting.

It displays a typical clock waveform with its associated clock information. You can enter or modify this information and save the final settings as long as the constraint information is consistent and defines the clock waveform completely. The tool displays errors and warnings if information is missing or incorrect.

To open the following Create Clock Constraint dialog box from the SmartTime Constraints Editor, choose Constraints > Clock.

Clock Source

Enables you to choose a pin from your design to use as the clock source.

The drop-down list is populated with all explicit clocks. You can also select the Browse button to access all potential clocks. The Browse button displays the Select Source Pins for Clock Constraint Dialog Box.

Clock Name

Specifies the name of the clock constraint. This field is required for virtual clocks when no clock source is provided.

Period

When you edit the period, the tool automatically updates the frequency value. The period must be a positive real number. Accuracy is up to 3 decimal places.

Frequency

When you edit the frequency, the tool automatically updates the period value.

The frequency must be a positive real number. Accuracy is up to 3 decimal places.

Starting Clock Edge Selector

Click the Up or Down arrow to use the rising or falling edge as the starting edge for the created clock.

Offset

Indicates the shift (in nanoseconds) of the first clock edge with respect to instant zero common to all clocks in the design.

The offset value must be a positive real number. Accuracy is up to 2 decimal places. Default value is 0.

Duty Cycle

This number specifies the percentage of the overall period that the clock pulse is HIGH.

The duty cycle must be a positive real number. Accuracy is up to 4 decimal places. Default value is 50%.

Add this clock to existing one with same source

Check this box if you want to add a new clock constraint on the same source without overwriting the existing clock constraint. The new clock constraint name must be different than the existing name. Otherwise, the new constraint will overwrite the existing one even if you check this box.

Comment

Enables you to save a single line of text that describes the clock constraints purpose.

See Also

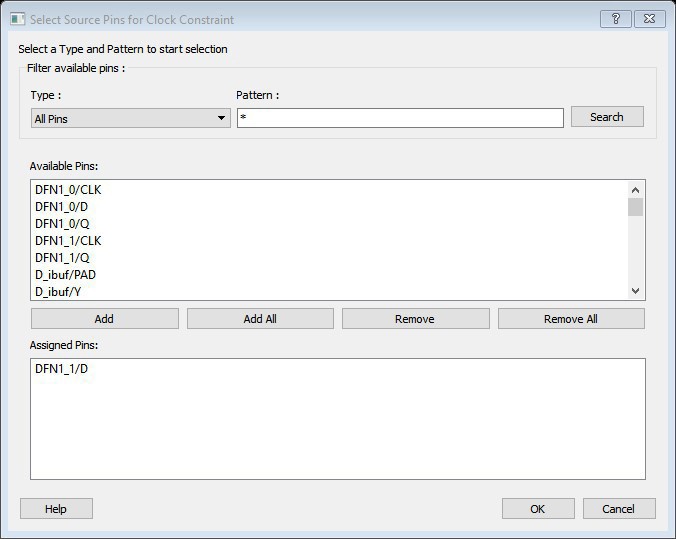

5.13.9 Select Source Pins for Clock Constraint Dialog Box

(Ask a Question)Use this dialog box to find and choose the clock source from the list of available pins.

To open the Select Source Pins for the following Clock Constraint dialog box from the SmartTime Constraints Editor, click the Browse button to the right of the Clock source field in the Create Clock Constraint dialog box.

- Type – Displays the Type of the Available Pins in the design. The Pin

Type options available for the Source are:

- All Pins

- Input Ports

- All Nets

- Pattern – The default is *, which is a wild-card match for all. You can specify any string value. Click Search to filter the available pins based on the specified pin Type and Pattern.

Available Pins

The list box displays the available pins. If you change the pattern value, the list box shows the available pins based on the filter.

Use Add, Add All to add the pins from the Available Pins list to Assigned Pins or Remove, Remove All to delete the pins from the Assigned Pins list.

Assigned Pins

Displays pins selected from the Available Pins list. Select Pins from this list and click OK to add the Source Pins for Clock Constraint.

See Also

5.13.10 Specifying Clock Constraints

(Ask a Question)Specifying clock constraints is the most effective way to constrain and verify the timing behavior of a sequential design. Use clock constraints to meet your performance goals.

To specify a clock constraint:

- Add the constraint in the editable constraints grid or open the Create Clock Constraint dialog box using one of the following methods:

- Click the icon in the Constraints Editor.

- Right-click the Clock in the Constraint Browser and choose Add Clock Constraint.

- Double-click Clock in the Constraint Browser.

- Choose Clock from the

Constraints drop-down menu (Constraints > Clock).

The following Create Clock Constraint dialog box appears.

Figure 5-244. Create Clock Constraint Dialog Box

- Click the

- Select the pin to use as the clock source. You

can click the Browse button to display the following 5.13.9 Select Source Pins for Clock Constraint Dialog Box.Note: Do not select a source pin when you specify a virtual clock. Virtual clocks can be used to define a clock outside the FPGA that is used to synchronize I/Os.

Use the Choose the Clock Source Pin dialog box to display a list of source pins from which you can choose. By default, it displays the explicit clock sources of the design. To choose other pins in the design as clock source pins, select Filter available objects - Pin Type as Explicit clocks, Potential clocks, All Ports, All Pins, All Nets, Pins on clock network, or Nets in clock network. To display a subset of the displayed clock source pins, you can create and apply a filter.

Multiple source pins can be specified for the same clock when a single clock is entering the FPGA using multiple inputs with different delays.

- Click OK to save these dialog box settings.

- Specify the Period in nanoseconds (ns) or Frequency in megahertz (MHz).

- Modify the Clock Name. The name of the first clock source is provided as default.

- Modify the Duty cycle, if needed.

- Modify the Offset of the clock, if needed.

- Modify the first edge direction of the clock, if needed.

- Select the check box for Add this clock to an existing one with the same source, if needed.

- Click OK. The new constraint appears in

the Constraints List.Note: When you choose File > Save, the Timing Constraints Editor saves the newly created constraint in the database.

5.13.10.1 Create Generated Clock Constraint Dialog Box

(Ask a Question)Use this dialog box to specify generated clock constraint settings.

It displays a relationship between the clock source and its reference clock. You can enter or modify this information and save the final settings as long as the constraint information is consistent. The tool displays errors and warnings if the information is missing or incorrect.

To open the following Create Generated Clock Constraint dialog box from the SmartTime Constraints Editor, choose Constraints > Generated Clock.

Clock Pin

Enables you to choose a pin from your design to use as a generated clock source.

The drop-down list is populated with all unconstrained explicit clocks. You can also select the Browse button to access all potential clocks and pins from the clock network. The Browse button displays the Select Generated Clock Source dialog box.

Reference Pin

Enables you to choose a pin from your design to use as a generated reference pin. You can select the Browse button to access all the available reference pins. The Browse button displays the Select Generated Clock Reference dialog box.

Generated Clock Name

Specifies the name of the Generated clock constraint. This field is required for virtual clocks when no clock source is provided.

Generated Frequency

Specify the values to calculate the generated frequency: a multiplication factor and/or division factor (must be positive integers) is applied to the reference clock to compute the generated clock.

Generated Clock Edges

Frequency of the generated clock can also be specified by selecting the Generated Clock Edges option. Specify the integer values that represent the edges from the source clock that form the edges of the generated clock.

Three values must be specified to generate the clock. If you specify less than three, a tooltip indicates an error. The following example shows how to specify the clock edges.

If LSB is the generated clock from CLK clock source, the edge values must be [1 3 5].

If MSB is the generated clock from CLK clock source, the edge values must be [1 5 9].

Edge Shift

Specify a list of three floating point numbers that represents the amount of shift, in library time units, that the specified edges are to undergo to yield the final generated clock waveform. These floating-point values can be positive or negative. Positive value indicates a shift later in time, while negative indicates a shift earlier in time.

For example, an edge shift of {1 1 1} on the LSB generated clock, will shift each derived edge by 1 time unit. To create a 200 MHz clock from a 100 MHz clock, use edge { 1 2 3} and edge shift {0 -2.5 -5.0}

Generated Waveform

Specify whether the generated waveform is the same or inverted with respect to the reference waveform. Click OK.

Phase

This field is primarily used to report the information captured from the CCC configuration process, and when constraint is auto-generated. Meaningful phase values are: 0, 45, 90, 135, 180, 225, 270, and 315. This field is used to report the information captured from the CCC configuration process, and when the constraint is auto-generated.

PLL Output

This field refers to the CCC GL0/1/2/3 output that is fed back to the PLL (in the CCC). This field is primarily used to report the information captured from the CCC configuration process, and when constraint is auto-generated.

PLL Feedback

This field refers to the way in which the GL/0/1/2/3 output signal of the CCC is connected to the PLL's FBCLK input. This field is primarily used to report the information captured from the CCC configuration process, and when constraint is auto-generated.

Add Clock to Existing Clock

Specifies that the generated clock constraint is a new clock constraint in addition to the existing one at the same source. The name of the clock constraint must be different from the existing clock constraint. When this option is selected, master clock must be specified.

Master Clock

Specifies the master clock used for the generated clock when multiple clocks fan into the master pin. It can be selected from the drop-down menu. This option is used in conjunction with the add option of the generated clock.

Comment

Enter a single line of text that describes the generated clock constraints purpose.

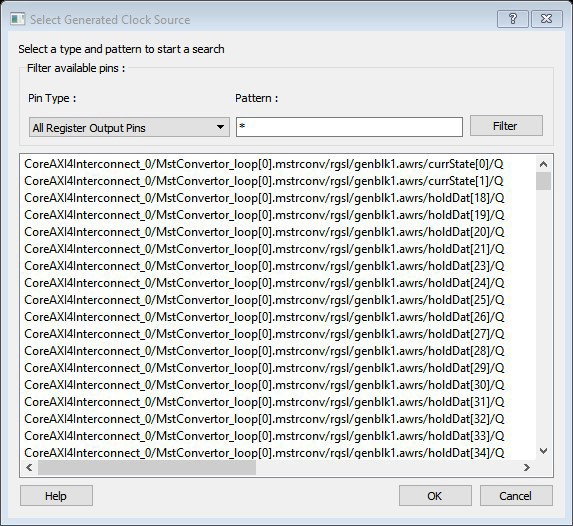

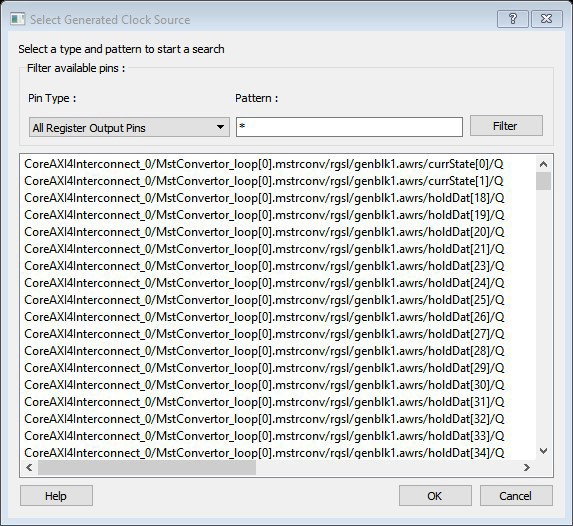

5.13.10.2 Select Generated Clock Source Dialog Box

(Ask a Question)Use this dialog box to find and choose the generated clock source from the list of available pins.

To open the following Select Generated Clock Source dialog box from the Timing Constraints Editor, open the Create Generated Clock Constraint dialog box and click the Browse button for the Clock Pin.

-

Pin type – Displays the Available Pin types. The Pin Type options for Generated Clock Source are:

- Output Ports

- All Register Output Pins

- All Pins

- All Nets

- Input Ports

-

Pattern – The default pattern is *, which is a wild-card match for all. You can specify any string value.

Select Filter to filter the available pins based on the specified Pin Type and Pattern.

The list box displays the list of available pins based on the filter. Select the pins from the list and click OK to select the Generated Clock Source Pin.

5.13.11 Specifying Generated Clock Constraints

(Ask a Question)Specifying a generated clock constraint enables you to define an internally generated clock for your design and verify its timing behavior. Use generated clock constraints and clock constraints to meet your performance goals.

To specify a generated clock constraint:

- Open the Create Generated Clock Constraint dialog box using one of the following

methods:

- Click the icon.

- Right-click the Generated Clock in the Constraint Browser and choose Add Generated Clock.

- Double-click the Generated

Clock Constraints grid. The following Create Generated Clock Constraint

dialog box appears.

Figure 5-248. Create Generated Clock Constraint

- Click the

- Select a Clock Pin to use as

the generated clock source. To display a list of available generated clock source

pins, click the Browse button. The following Select Generated Clock Source dialog box appears.

Figure 5-249. Select Generated Clock Source Dialog Box

- Specify a Reference Pin. To display a list of available clock reference pins, click the Browse button. The Select Generated Clock Reference dialog box appears.

- Specify the Generated Clock Name (optional).

- Specify the values to calculate the generated frequency: a multiplication factor and/or a division factor (both positive integers).

- Specify the orientation of the generated clock edges based on the reference edges by entering values for the edges and the edge shifts. This is optional.

- Specify the first edge of the generated waveform either same as or inverted with respect to the reference waveform.

- Specify the PLL output and PLL feedback pins if an External feedback is used to generate the clock.

- Specify the Phase shift applied by the PLL in degrees.

- Specify the Master Clock, if you want to add this to an existing one with the same source.

- Click OK. The new constraint appears in the Constraints List.

Tip: From the File menu, choose Save to save the newly created constraint in the database.

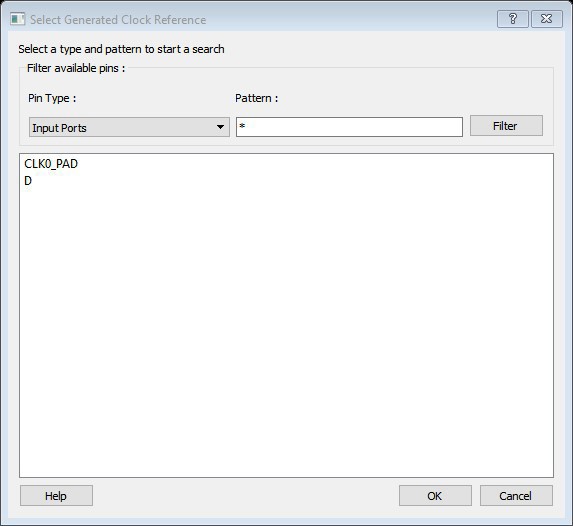

5.13.11.1 Select Generated Clock Reference Dialog Box

(Ask a Question)Use this dialog box to find and choose the generated clock reference pin from the list of available pins.

To open the following Select Generated Clock Reference dialog box from the SmartTime Constraints Editor, open the Create Generated Clock Constraint Dialog Box dialog box and click the Browse button for the Clock Reference.

- Pin type : Displays the

Available Pin types. The Pin Type options for Generated Clock Reference are:

- Input Ports

- All Pins

- Pattern: The default

pattern is *, which is a wild-card match for all. You can specify any string

value.

Select Filter to filter the available pins based on the specified Pin Type and Pattern.

The list box displays the list of available pins based on the filter. Select the pins from the list and click OK to select the Generated Clock Reference Pin.

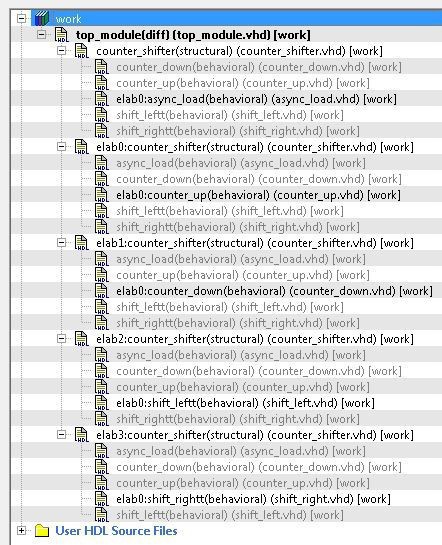

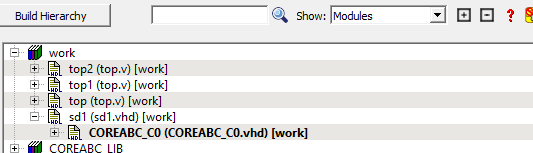

5.13.12 Design Hierarchy in the Design Explorer

(Ask a Question)The Design Hierarchy tab displays a hierarchical representation of the design based on the source files in the project. It also displays elaborated hierarchy constructed by propagating correct values for parameters and generics. The software continuously analyzes the source files and updates the content. The following Design Hierarchy tab displays the structure of the modules and components as they relate to each other along with parameter/generic names and its values on the tooltip for which the module is instantiated. It also displays architecture name for a given entity and Configuration for VHDL modules.

A module can have multiple elaborations depending on the different parameters/generics

used in the instantiation of the module and all these elaborated modules will be shown

in the Design Hierarchy. The parameterized instantiated module will be shown as

elab<num>:<modulename>.

Modules are instantiated with their actual names in the SmartDesign. If a module with elaborated name in the Design Hierarchy must be instantiated in the SmartDesign, an instance of the original module is created in the SmartDesign. The following figure shows the design hierarchy with elaborated modules.

Modules which are not part of the elaboration will be shown in the complete hierarchy but they remain grayed out. When you create a core from a module, all the elaborated modules of that module will be shown as HDL+ core modules. You can get the parameter value of an elaborated module by selecting Show Module parameters on the right-click menu of the elaborated module.

Note: Synthesis output will be the same for different elaborations of the same module, that is elab0:module1 and elab1:module1 will have the same synthesis output. When one of the elaborated modules is set as root, all the elaborations will be highlighted in the Design Hierarchy, as shown in the following figure.

You can change the display mode of the Design Hierarchy by selecting Components or Modules from the Show drop-down list. The components view displays the entire design hierarchy; the modules view displays only schematic and HDL modules.

You can build the Design Hierarchy and Simulation Hierarchy by clicking the Build Hierarchy button.

A yellow icon

The file name (the file that defines the block) appears next to the block name in parentheses.

To view the location of a component, right-click and choose Properties. The Properties dialog box displays the path name, created date, and last modified date.

All integrated source editors are linked with the SoC software. If a source is modified and the modification changes the hierarchy of the design, the Build Hierarchy automatically updates to reflect the change.

If you want to update the Design Hierarchy, from the View menu, choose Refresh Design Hierarchy.

To open a component:

Double-click a component in the Design Hierarchy to open it. Depending on the block type and design state, several possible options are available from the right-click menu. You can instantiate a component from the Design Hierarchy to the SmartDesign Canvas. See the SmartDesign User Guide for more information.

Icons in the Hierarchy indicate the type of component and the state, as shown in the following table.

| Icon | Description |

|---|---|

|

|

SmartDesign component |

|

|

SmartDesign component with HDL netlist not generated |

|

|

IP core was instantiated into SmartDesign but the HDL netlist is not generated |

|

|

Core |

|

|

Error during core validation |

|

|

Updated core available for download |

|

|

HDL netlist |

|

|

Shows ungenerated components |

|

|

Shows unknown modules |

|

|

Expands all the files and folders in the Design Hierarchy |

|

|

Collapses all the files and folders in the Design Hierarchy |

|

|

Finds the files in the Design Hierarchy |

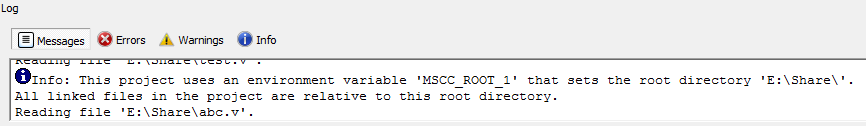

Linked Files with Relative Path in Design Hierarchy with Environment Variable

The following figure shows linked files that have a relative path in the design hierarchy with the Environment variable. Linked files that are in a drive different to the drive specified in Environment variable path are shown as absolute files in Windows.

Properties of file in Design Hierarchy shows Relative Path and Relative Path root directory

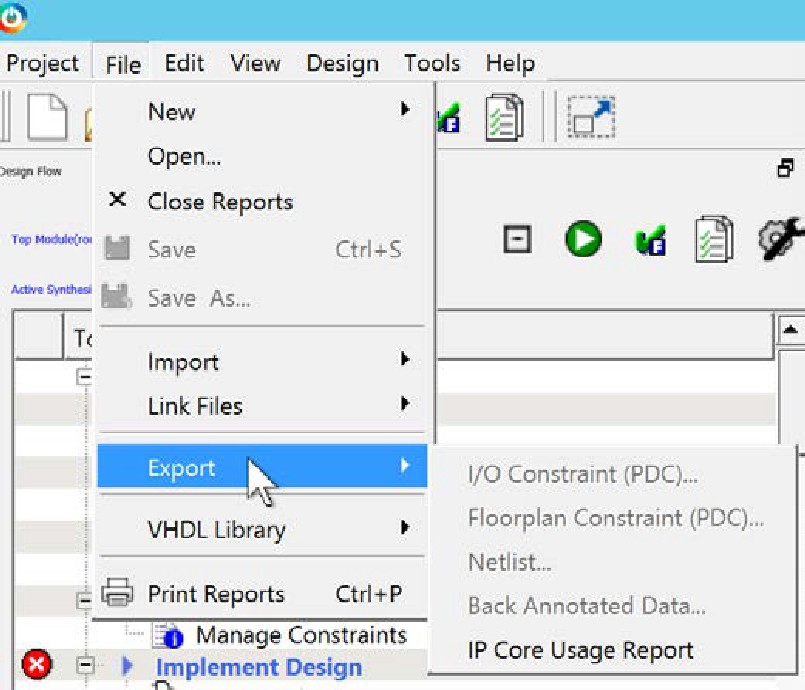

5.13.13 Digest File

(Ask a Question)You can verify which bitstream file was programmed on the devices by running the VERIFY or VERIFY_DIGEST actions on each device that was programmed. This is a costly and time-consuming process. To speed up the verification process, digests are printed during bitstream generation and bitstream programming.

These digests can be compared to verify that all the devices were programmed with the correct bitstream file.

The bitstream file is divided into three major component sections: FPGA fabric, eNVM, and Security. A valid bitstream will contain a combination of any of the three primary bitstream components.

Use Case

When a customer creates a design in Libero and then exports the STAPL file (for FlashPro) or programming job (for FlashPro Express), the digest of each of the primary components is printed in the Libero log window and saved in a digest file under the export folder. The digest file is a text file containing the bitstream component name with its corresponding digest. The name of the digest file will match the name of the STAPL/programming job exported, and will be appended with a “.digest” extension.

The customer then sends the STAPL/programming job to a production programming house. Now, when the devices are programmed, the digest of each of the primary components is printed in the log window. The production programming house saves the log files and sends the devices along with log files back to the customer. The customer can verify that the correct design was programmed on the device by matching the digests in the log file with *.digest file under the Libero export folder.

Digest printed during programming (same as in *.digest file) is bitstream payload digest. It is meant for device to confirm that it receives the correct bitstream payload.

Digest exported from DEVICE_INFO is the digest of the actual memory content. It does not have other metadata that is included in the encrypted bitstream payload, so it will be different than one generated during programming.

See Also

5.13.14 Design Rules Check

(Ask a Question)The Design Rules Check runs automatically when you generate your SmartDesign; the results appear in the Reports tab. You can also initiate a Design Rules Check by clicking on the

To view the results, from the Design menu, choose Reports.

- Status displays an icon to

indicate if the message is an error or a warning (as shown in the

following figure). Error messages are shown with a small red sign

and warning messages with a yellow exclamation point.

- Message identifies the specific error/warning (see the following list); click any message to see where it appears on the Canvas.

- Details provides information related to the Message.

Message Types:

Unused Instance - You must remove this instance or connect at least one output pin to the rest of the design.

Out-of-date Instance - You must update the instance to reflect a change in the component referenced by this instance.

Undriven Pin - To correct the error you must connect the pin to a driver or change the state, that is, tie LOW (GND) or tie HIGH (VCC).

Floating Driver - You can mark the pin unused if it is not being used in the current design. Pins marked unused are ignored by the Design Rules Check.

Unconnected Bus Interface - You must connect this bus interface to a compatible port because it is required connection.

Required Bus Interface Connection – You must connect this bus interface before you can generate the design. These are typically silicon connection rules.

Exceeded Allowable Instances for Core – Some IP cores can only be instantiated a certain number of times for legal design because of silicon limitations. You must remove the extra instances.

Incompatible Family Configuration – The instance is not configured to work with this project’s Family setting. Either it is not supported by this family, or you need to re-instantiate the core.

Incompatible Die Configuration – The instance is not configured to work with this project’s Die setting. Either it is not supported or you need to reconfigure the Die configuration.

No RTL License, No Obfuscated License, No Evaluation License – You do not have the proper license to generate this core. Visit the Microchip Licensing page to obtain the necessary license.

No Top-level Ports - There are no ports on the top-level. To auto-connect top-level ports, right-click the Canvas and choose Auto-connect.

Self-Instantiation - A component cannot instantiate itself. This is reported only in the Log/Message Window.

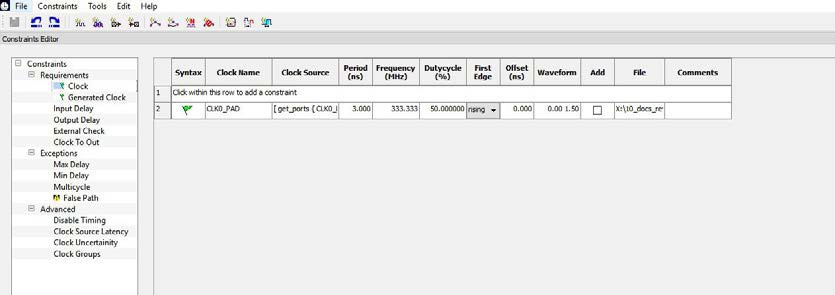

5.13.15 Editable Constraints Grid

(Ask a Question)The Constraints Editor enables you to add, edit, and delete.

To add a new constraint:

- Select a constraint type from the constraint browser.

- Enter the constraint values in the first row and click the green check mark to apply your changes. To cancel the changes, press the red cancel mark.

- The new constraint is added to the Constraint List. The green syntax flag indicates that the constraint was successfully checked.

To edit a constraint:

- Select a constraint type from the constraint browser.

- Select the constraint, edit the values, and click the green check mark to apply your changes. To cancel the changes, press the red cancel mark. The green syntax flag indicates that the constraint was successfully checked.

To delete a constraint:

- Select a constraint type from the constraint browser.

- Right-click the constraint you want to delete and choose Delete Constraint.

5.13.16 Files Tab and File Types

(Ask a Question)The Files tab displays all the files associated with your project, listed in the directories in which they appear.

Right-clicking a file in the Files tab provides a menu of available options specific to the file type. You can delete files from the project and the disk by selecting Delete from the right-click menu.

You can instantiate a component by dragging the component to a SmartDesign Canvas or by selecting Instantiate in SmartDesign from the right-click menu. See the SmartDesign User Guide for more details.

You can configure a component by double-clicking the component or by selecting Open Component from the right-click menu.

File Types

When you create a new project in the Libero SoC it automatically creates new directories and project files. Your project directory contains all your 'local' project files. If you import files from outside your current project, the files must be copied into your local project folder (The Project Manager enables you to manage your files as you import them).

Depending on your project preferences and the Libero SoC version you installed, the software creates directories for your project.

The top-level directory (<project_name>) contains your PRJ file; only one PRJ file is enabled for each Libero SoC project.

- component directory - Stores your SmartDesign components (SDB and CXF files) for your Libero SoC project.

- constraint directory - All your constraint files (SDC, PDC).

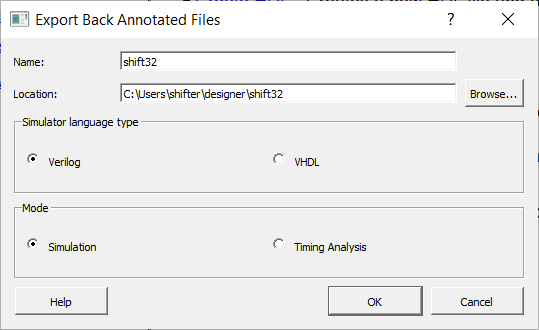

- designer directory - *_ba.sdf, *_ba.v(hd), STP, TCL (used to run designer), designer.log (log file) hdl directory - all hdl sources. *.vhd if VHDL, *.v and *.h if Verilog, *.sv if SystemVerilog simulation directory - meminit.dat, modelsim.ini files.

- smartgen directory - GEN files and LOG files from generated cores.

- stimulus directory - BTIM and VHD stimulus files.

- synthesis directory - *.edn, *_syn.prj (Synplify log file), *.srr (Synplify log file), *.tcl (used to run synthesis) and many other files generated by the tools (not managed by Libero SoC).

- tooldata directory - includes the log file for your project with device details.

5.13.17 Importing Files

(Ask a Question)Anything that describes your design, or is needed to program the device, is a project source. These might include schematics, HDL files, simulation files, testbenches, and so on. Import these source files.

To import a file:

- From the File menu, choose Import Files.

- In Files of type, choose the file type.

- In Look in, navigate to the drive/folder where the file is located.

- Select the file to import and click

Open.Note: You cannot import a Verilog File into a VHDL project and vice versa.

| File Type | File Extension |

|---|---|

Behavioral and Structural VHDL; VHDL Package | *.vhd, *.vhdl |

Design Block Core | *.gen |

Verilog Include | *.h |

Behavioral and Structural Verilog | *.v, *.sv |

Netlist Verilog | *.vm |

Stimulus | *.vhd, * .vhdl, *.v, *.sv |

Memory file | *.mem |

Components (Designer Blocks, Synplify DSP) | *.cxf |

MSS Components | *.cxz |

5.13.18 Layout Error Message: layoutg4NoValidPlacement

(Ask a Question)This is a generic error produced by the placer when it is unable to place a design. The most common cause for this failure is that the placer was unable to find a solution, which could fit the design into the chip, either because the design is close to maximum utilization, or logic cannot be fit into user-defined region constraints.

If Libero is unable to find a legal placement, a list of unplaced cells will be provided in the log. The cells in this list might not be the cause of the placement problem; it is quite possible that some other constrained block of logic was placed first and now prohibits further placement. However, starting with the unplaced cell list is the easiest and most likely course:

- The simplest potential solution is to remove all placement constraints of the unplaced cells, and re-run Place and Route.

However, the cells in this list might not be the cause of the placement problem; it is quite possible that some other constrained block of logic which was placed first and now prohibits further placement. If removing the placement constraints on the unplaced cells fails.

- Remove all region constraints and re-run Place

and Route. Some designers make it a practice to put all their region constraints in

a single, separate PDC file; in which case they need to disable that file.

- If this Place and Route re-run still fails, there might be wider issues with the design's size and complexity that cannot be addressed by changes to Place and Route options.

- If the unconstrained Place

and Route re-run succeeds, then the you must add back constraints a few

regions at a time in order of "simplicity". Usually, big regions with lots

of free space are "simpler" for the placer, whereas tall/narrow regions with

high utilization are "harder". Re-run Place and Route with each constraint

restoration and repeat the process until the failing region(s) is

identified.

Depending on requirements, the failing region might be handled by removing or changing its constraints, or revising its design to use less resources.

You can also re-run the Placer in high-effort mode. Applying high-effort mode to a design which is very full can incur additional runtime and can produce a placement solution that might not meet tight timing constraints because the placer will aggressively attempt to fit the design. In practice, customers are encouraged to apply the previous suggestions first; and utilize high-effort mode only when other approaches are exhausted.

5.13.19 Layout Error Message: layoutg4DesignHard

(Ask a Question)This design is very difficult to place, and high-effort techniques were required to fit it. This might lead to increased layout runtime and diminished timing performance.

This message typically appears in designs with high utilization — a very full design, or a design with region constraints which are, themselves, very full. It can also occur in designs with moderate utilization but with numerous, long carry chains.

No immediate action is required. However, if this notice is observed during Layout, the resultant performance of the design and the runtime of the Layout tools might not be optimal, and there is a strong possibility that reducing the size of the design, or relaxing region and floorplanning constraints, will help to improve timing closure and runtime.

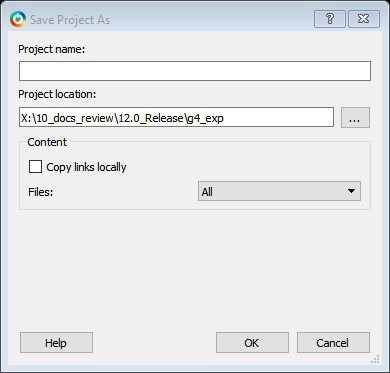

5.13.20 Save Project As Dialog Box

(Ask a Question)The Save Project As dialog box enables you to save your entire project with a new name and location. To access this dialog box, choose Save Project As from the Project menu.

Project Name

Type the project name for your modified project.

Project Location

Accept the default location or Browse to the new location where you can save and store your project. All files for your project are saved in this directory.

Content

Copy links locally - Check this check box to copy the links from your current project into your new project. If you do not check this check box, the links will not be copied and you must add them manually.

Files

- All - Includes all your project and source files; the state of the project is retained.

- Project files only - Copies only the project-related information required to retain the state of the project.

- Source files only - Copies all the source files into the specified location. This means the configuration of all the tools in the tool chain is retained but the states are not. Source files means constraint information and component information available in the component, hdl and smartgen directories.

Files are saved as shown in the following table.

| Folder Name | Files | ||

|---|---|---|---|

| All | Project | Source | |

component | All Files | All Files | All Files |

constraint | All Files | All Files | All Files |

hdl | All Files | All Files | All Files |

|

stimulus |

All Files |

All Files |

All Files |

|

smartgen |

All Files |

All Files |

All Files |

|

firmware |

All Files |

All Files |

All Files |

|

CoreConsole |

All Files |

All Files |

All Files |

|

SoftConsole/Keil/IAR |

All Files |

All Files |

All Files |

|

Phy_Synthesis |

All Files |

All Files |

Not Copied |

|

simulation |

All Files |

*.ini, *.bfm, *.do., *.vec |

*.ini, *.bfm, *.do., *.vec |

|

synthesis |

All Files |

*.edn, *.vm, *.sdc, *.so, *.prj, *.srr, *.v, run_options.txt, synplify.log |

*.prj files |

|

Designer/impl1 |

All Files |

All Files |

*.ide_des files |

|

Designer/<root> |

All Files |

All Files |

Not Copied |

|

tooldata |

All Files |

All Files |

All Files |

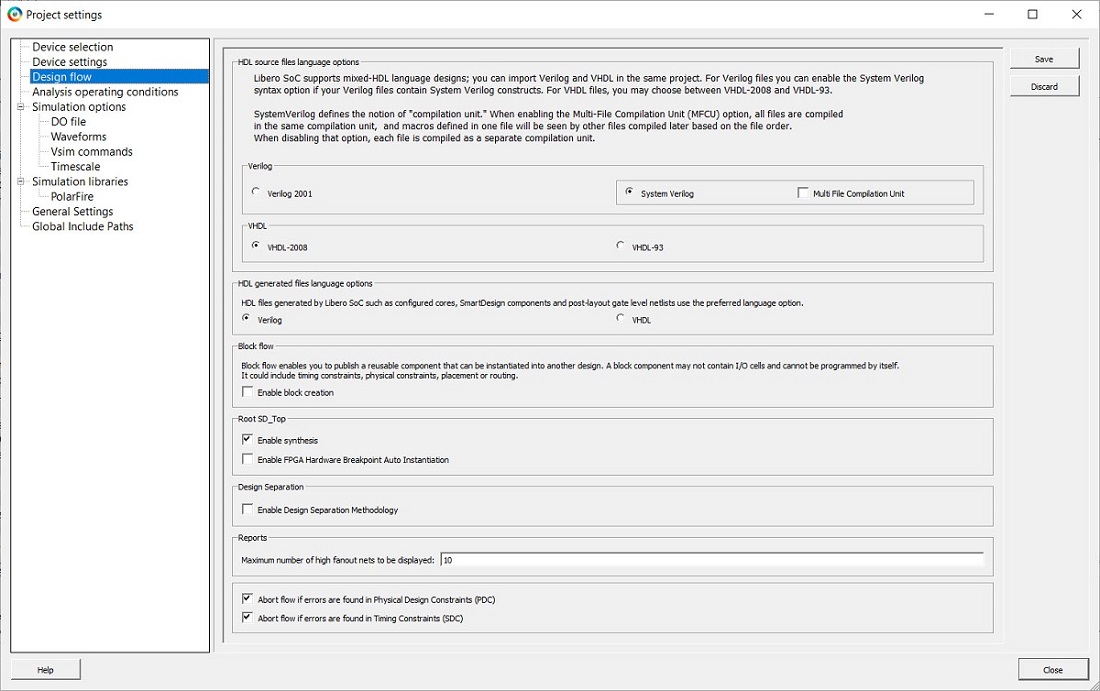

5.13.21 Project Settings Dialog Box

(Ask a Question)The Project Settings dialog box enables you to modify your Device, HDL, and Design Flow settings and your Simulation Options. In Libero SoC, from the Project menu, click Project Settings.

Device Selection

Sets the device Die and Package for your project. See the New Project Creation Wizard - Device Selection page for a detailed description of the options.

Device Settings

Default I/O Technology - Sets all your I/Os to a default value. You can change the values for individual I/Os in the I/O Attributes Editor.

System controller suspended mode. If the System controller suspended mode is enabled in any PolarFire design, the following operations will not be available during normal operation. For more information, refer to the System Services section in the PolarFire FPGA Security User Guide (UG0753).

- All System Controller services requested after power-up is complete and the System Controller is suspended

- System controller generated Tamper flags

- Device reset and zeroization Tamper responses

- SPI-Master In-Application Programming (IAP)

- SPI-Slave programming mode

For RT PolarFire devices, the System Controller suspended mode is enabled by default for all new RT PolarFire projects. If the System controller suspended mode is disabled, it increases vulnerability to radiation single event effects in the System controller.

Design Flow

See the Project Settings: Design flow for more information.

Analysis Operating Conditions

Sets the Operating Temperature Range, the Core Voltage Range, and Default I/O Voltage Range from the pick lists provided. Typical values are COM/IND/MIL; but others are sometimes defined.

Only EXT and IND ranges are available for PolarFire at present.

Once the "Range" value is set, the Minimum/Typical/Maximum values for the selected range are displayed.

These settings are propagated to Verify Timing, Verify Power, and Backannotated Netlist for you to perform Timing/Power Analysis.

Simulation Options and Simulation Libraries

Sets your simulation options. See the Project Settings: Simulation Options topic for more information.

5.13.21.1 Project Settings: Simulation - Options and Libraries

(Ask a Question)Using this dialog box, you can set change how Libero SoC handles Do files in simulation, import your own Do files, set simulation run time, and change the DUT name used in your simulation. You can also change your library mapping.

To access this dialog box, from the Project menu choose Project Settings and click to expand Simulation options or Simulation libraries.

For Simulation options click the option you wish to edit: DO file, Waveforms, Vsim commands, Timescale. For Simulation libraries click on the library you wish to change the path for.

DO file:

- Use automatic DO file - Select if you want the Project Manager to automatically create a DO file that will enable you to simulate your design.

- Simulation Run Time - Specify how long the simulation must run. If the value is 0, or if the field is empty, there will not be a run command included in the run.do file.

- Testbench module name - Specify the name of your testbench entity name. Default is “testbench,” the value used by WaveFormer Pro.

- Top Level instance name - Default is <top_0>, the value used by WaveFormer Pro. The Project Manager replaces <top> with the actual top-level macro when you runsimulation(presynth/postsynth/postlayout).

- Generate VCD file - Check the check box to generate a VCD file.

- VCD file name - Specifies the name of your generated VCD file. The default is power.vcd; click power.vcd and type to change the name.

- User defined DO file - Enter the DO file name or click the browse button to navigate to it.

- DO command parameters - Text in this field is added to the DO command.

Waveforms

- Include DO file - Including a DO file enables you to customize the set of signal waveforms that will be displayed in ModelSim.

- Display waveforms for - You can display signal waveforms for either the top-level testbench or for the design under test. If you select top-level testbench then Project Manager outputs the line 'addwave /testbench/*' in the DO file run.do. If you select DUT then Project Manager outputs the line 'add wave /testbench/DUT/*' in the run.do file.

- Log all signals in the design - Saves and logs all signals during simulation.

- Resolution - The default is 1ps. Some custom simulation resolutions might not work with your simulation library. Consult your simulation help for more information on how to work with your simulation library and detect infinite zero-delay loops caused by high resolution values.

- Additional options - Text entered in this field is added to the vsim command.

- SRAM ECC Simulation -

Two options can be added to specify the simulated error and correction probabilities of all ECC SRAMs in the design.

-gERROR_PROBABILITY=<value>, where 0 <= value <= 1-gCORRECTION_PROBABILITY=<value>, where 0 <= value <= 1

- During Simulation, the

SB_CORRECTandDB_DETECTflags on each SRAM block will be raised based on generated random numbers being below the specified<value>s. - When you run the Post-Layout Simulation Tool, a

run.do file is created, which consists of

information which needs to be sent to a simulator.

To run a simulation on a corner, you must select

one of the SDF corners along with the type of

delay needed from one of the options in SDF timing

delays section.

- SDF Corners:

- Slow Process, Low Voltage, and High Temperature

- Slow Process, Low Voltage, and Low Temperature

- Fast Process, High Voltage, and Low Temperature

- SDF Timing Delays:

- Minimum

- Typical

- Maximum

- Disable pulse filtering during SDF based simulations: This option disables the pulse filtering during SDF simulations.

- After the user selects the corner, appropriate files needed for

simulation are written in the run.do file as shown in the following

example.

vlog -sv -work postlayout “$(PROJECT_DIR)/designer/sd1/sd1_fast_hv_lt_ba.v” vsim -L PolarFire -L postlayout -t 1ps -sdfmax /sd1=$(PROJECT_DIR)/designer/sd1/sd1_fast_hv_lt_ba.sdf +pulse_int_e/1 +pulse_int_r/1 +transport _int_delays postlayout.sd1

- SDF Corners:

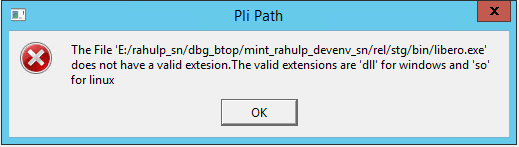

- To run a simulation on a design having Crypto

core, you need to enter the PLI path in the PLI

Path field. You can use the browse button to

select the appropriate file. After the file is

selected the PLI Path field is populated with the

path and file. You can also manually enter the

path in the PLI path field.

- Errors will be generated in case of wrong path or

wrong file extension as follows:

- If you enter a wrong PLI path and click on Save.

- If the user enters a wrong file extension, the

following error message is displayed.

- Errors will be generated in case of wrong path or

wrong file extension as follows:

- To compile all the files under System Verilog

Multi-File Compilation Unit (MFCU) mode, group

them based on the library. This applies to all the

.hdl files, simulation files, and core files. The

following code example provides a general syntax

to compile the files in System Verilog MFCU

mode.

vlog "+incdir+<incdir1>" "+incdir+<incdir2>" -sv -mfcu -work library1 "file1" "file2" "file3" vlog "+incdir+<incdir1>" "+incdir+<incdir2>" -sv -mfcu -work library2 "file4" "file5" "file6"

- SRAM ECC Simulation -

Timescale

- TimeUnit - Enter a value and select s, ms, us, ns, ps, or fs from the pull-down list, which is the time base for each unit. The default setting is ns.

- Precision - Enter a value and select s, ms, us, ns, ps, or fs from the pull-down list. The default setting is ps.

Simulation Libraries

- Restore Defaults- Sets the library path to default from your Libero SoC installation.

- Library path - Enables you to change the mapping for your simulation library (both Verilog and VHDL). Type the pathname or click the Browse button to navigate to your library directory.

5.13.21.2 Project Settings: Design Flow

(Ask a Question)To access the Design flow page, from the Project menu choose Project settings. From the Project settings window, select the Design flow from the left pane.

HDL Source Files Language Options

Libero SoC supports mixed-HDL language designs. You can import Verilog and VHDL in the same project.

You can set HDL to VHDL or Verilog. For VHDL, choose VHDL-2008 or VHDL-93. For Verilog, choose System Verilog (if your Verilog files contain System Verilog constructs) or Verilog 2001.

SystemVerilog defines the notion of "compilation unit." Enabling the Multi-File Compilation Unit (MFCU) option, compiles all the files in the same compilation unit, and macros defined in one file will be seen by other files compiled later based on the file order. Disable the option to compile each file as a separate compilation unit.

When a New Project is created, Multi-File Compilation Unit option is enabled by default. This option will be disabled/greyed out if Verilog-2001 option is selected.

- Verilog 2005 (IEEE Standard 1364-2005)

- Verilog 2001 (IEEE Standard 1364-2001)

- Verilog 1995 (IEEE Standard 1364-1995)

- SystemVerilog 2012 (IEEE Standard 1800-2012)

- VHDL-2008 (IEEE Standard 1076-2008)

- VHDL-93 (IEEE Standard 1076-1993)

HDL generated files language options

HDL files generated by Libero SoC can be set to use VHDL or Verilog. If there are no other considerations, it is generally recommended to use the same HDL language as you are using for HDL source files because it can reduce the cost of simulation licenses.

Block flow

Enable block creation - Enables you to create and publish design blocks (*.cxz files) in Libero SoC. Design blocks are low-level components that might have completed the Place and Route step and met the timing and power requirements. These low-level design blocks can be imported into a Libero SoC project and re-used as components in a higher level design. See Designing with Designer Block Components in the Online Help for more information.

Root <module_name>

Enable synthesis - Option to enable or disable synthesis for your root file; useful if you wish to skip synthesis on your root file by default.

Enable FPGA Hardware Breakpoint Auto Instantiation - The FPGA Hardware Breakpoint (FHB) Auto Instantiation feature automatically instantiates an FHB instance per clock domain that is using gated clocks (GL0/GL1/GL2/GL3) from an FCCC instance. The FHB instances gate the clock domain they are instantiated on. These instances can be used to force halt the design or halt the design through a live probe signal. Once a selected clock domain or all clock domains are halted, you can play or step on the clock domains, either selectively or all at once. FPGA Hardware Breakpoint controls in the SmartDebug UI provide control of the debugging cycle.

Reports

Maximum number of high fanout nets to be displayed - Enter the number of

high fanout nets to be displayed. The default value is 10. This

means the top 10 nets with the highest fanout will appear in the

<root>_compile_netlist_resource.xml>

report.

Abort Flow Conditions

Abort Flow if Errors are found in Physical Design Constraints (PDC) – Check this check box to abort Place and Route if the I/O or Floorplanning PDC constraint file contains errors.

Abort Flow if Errors are found in Timing Constraints (SDC) – Check this check box to abort Place and Route if the Timing Constraint SDC file contains errors.

Abort flow if 3.3 V I/Os are found in the design – Check this check box to abort Place and Route if 3.3 V I/Os are found in the design. This allows the tool to generate an error similar to the following. However, if the check box is unchecked, the Place and Route tool will generate the same error message as a warning without interrupting the design flow process.

Error: I/Os at 3.3 V are vulnerable to Single Event Latch-up at low LET levels. Review RT PolarFire radiation data at Microchip.com.

5.13.21.3 Project Settings: General Settings

(Ask a Question)Absolute/Relative path for linked files

Use either "absolute path for linked files" or "relative path for the linked files" for the files linked in the project. The path set in the environment variable is read only.

If "Use absolute path for linked files" option is selected, all the linked files are stored with the absolute path.

If "Use relative path for linked files "option is selected, the user is given an option to provide an environment variable that contains the root directory path that will be used as base location for the relative paths. All the files linked will be relative to the base location specified in environment variable by the user.

After you set the relative path and provides an environment variable that has a valid path, the following message appears in the log window.

This message can appear in the log window when the user:

- Opens a project that was created using relative path for linked files.

- Creates a project with relative path for linked files.

- Changes the environment variable from the project settings.

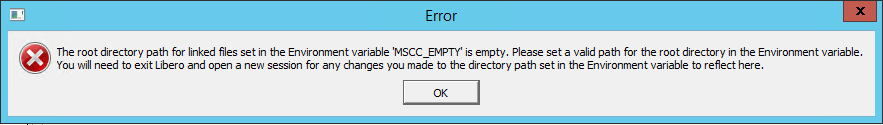

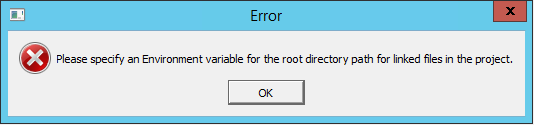

The environment variable set by the user is validated before proceeding. If the environment variable set by the user is not present or if it is set after starting Libero, the tool issues the following error.

Error message: The Environment variable <env_variable_name> specified for the root directory path for linked files is not defined/set in your environment. Ensure to set the appropriate root directory path in the Environment variable before you open Libero. Exit Libero and open a new session for any changes you made to the directory path set in the Environment variable to reflect here.

- Empty path in Environment variable

Error message: The root directory path for linked files set in the Environment variable <env_variable_name> is empty. Set a valid path for the root directory in the Environment variable. Exit Libero and open a new session for any changes you made to the directory path set in the Environment variable to reflect here.

- Inaccessible path in environment variable

Error message: The root directory path <env_variable_directory> for linked files set in the Environment variable <env_variable_name> does not exist. Set a valid accessible directory path in the Environment variable. You will need to exit Libero and open a new session for any changes you made to the directory path set in the Environment variable to reflect here.

- Project location is set as root directory in environment variable

Error message: The root directory path <env_variable_path> for the linked files set in the Environment variable

<env_variable_name> must not match with the current project directory path. Set a different directory path in the Environment variable. You need to exit Libero and open a new session for any changes you made to the directory path set in the Environment variable to reflect here.

- Project settings are saved by

selecting relative path and the environment variable is not specified

Error message: Specify an Environment variable for the root directory path for linked files in the project.

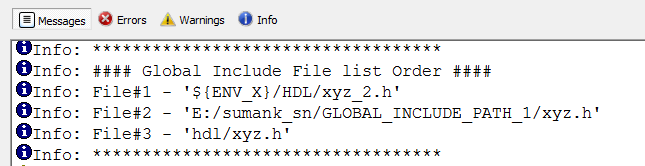

5.13.21.4 Project Settings: Global Include Paths

(Ask a Question)Example:

If a user has a defines file which exists in all the three paths – source file path(default), global_inlcude_path_1 and global_include_path_2; the order of priority of files will be as follows:

- Source file path(default)

- Global_include_path_1

- Global_inlcude_path_2

Absolute and Relative paths in Global Include Paths

You can specify both relative and absolute files in global include paths. Example -

Absolute Path : { E:/User/GLOBAL_INCLUDE_PATH_1 } Relative Path: { ../hdl/GLOBAL_INCLUDE_PATH_1 }

Relative Path with respect to Environment Variable: { ${ENV_VAR}/GLOBAL_INCLUDE_PATH_1 }

Here, the environment variable must be the one used in absolute ad relative paths options only.

- Changing the Global Include Paths will invalidate the Design Hierarchy but not the Design flow.

- Change in content of Include Files present in

Global Include Paths has impact as in the following cases:

- Case 1: If the Global Include Path is part of the project – Design flow will be invalidated.

- Case 2: If the Global Include Path is outside the project – Design flow will not be invalidated.

The files are audited only if they are part of the project.

5.13.22 Global Include Files

(Ask a Question)This option facilitates the users to provide global include file/s in Libero and manage how these files are sent to downstream tools occurring in Design Flow process.

Libero GUI facilitates user to provide Global Include Files. On right clicking a file in Design Hierarchy view, user can either set a file as global include by selecting Set Global Include option or unset a file as global include by selecting Unset Global Include option.

Linked files can also be set as Global Include files. The files that are set are highlighted in Design hierarchy view as shown in the following figure.

The selected order of global include files is shown in Info tab in log window:

Setting Global Include File will use System Verilog MFCU mode internally. An info message will be generated in the log window as below:

Info: Global Include file requires System Verilog setting to be in MFCU mode. Enabling Multi File Compilation Unit internally.

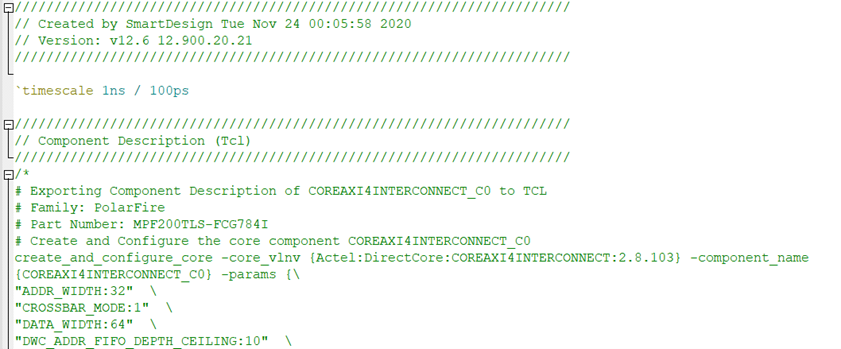

5.13.23 Create and Configure Core Component

(Ask a Question)- The user can create, configure, and generate a component for any core in the Libero SoC Catalog window.

- Select a core in the Catalog window by double clicking or right clicking on it and choose the option 'Configure core'.

- Specify a name to the core component to be created in the pop-up dialog box.

- The core's configurator window appears where the user can specify any desired configuration and click on the OK button to generate the core component.

Once the core component is created and generated, the component related files like the generated HDL netlist file are also generated to the directory <project directory>/component/work/<component_name>. The generated HDL netlist file of the core component now contains the component description/configuration information in Tcl as comments. These comments also include Family Name and Part Number of the device used. The following figure shows a sample Tcl component description of the core COREAXI4INTERCONNECT.

5.13.24 Search in Libero SoC

(Ask a Question)Search options vary depending on your search type.

To find a file:

- Use CTRL + F to open the Search window.

- Enter the name or part of name of the object you wish to find in the Find field. '*' indicates a wildcard, and [*-*] indicates a range, such as if you search for a1, a2, ... a5 with the string a[1-5].

- Set the Options for your search; options vary depending on your search type.

- Click Find All (or

Next if searching Text).

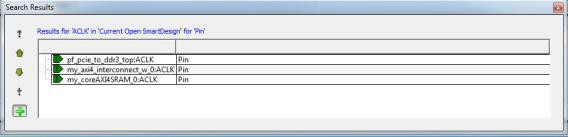

Searching an open text file, Log window, or Reports highlights search results in the file itself. All other results appear in the Search Results window (as shown in the following figure).

Match case: Select to search for case-sensitive occurrences of a word or phrase. This limits the search so it only locates text that matches the upper- and lowercase characters you enter.

Match whole word: Select to match the whole word only.

Currently Open SmartDesign

Searches your open SmartDesign, returns results in the Search window.

Type: Choose Instance, Net or Pin to narrow your search.

Query: Query options vary according to Type.

| Type | Query Option | Function |

|---|---|---|

Instance | Get Pins | Search restricted to all pins |

Get Nets | Search restricted to all nets | |

Get Unconnected Pins | Search restricted to all unconnected pins | |

Net | Get Instances | Searches all instances |

Get Pins | Search restricted to all pins | |

Pin | Get Connected Pins | Search restricted to all connected pins |

Get Associated Net | Search restricted to associated nets | |

Get All Unconnected Pins | Search restricted to all unconnected pins |

Currently Open Text Editor

- Find All: Highlights all finds in the text file.

-

Next: Proceed to next instance of found text.

-

Previous: Proceed to previous instance of found text.

-

Replace with: Replaces the text you searched with the contents of the field.

-

Replace: Replaces a single instance.

-

Replace All: Replaces all instances of the found text with the contents of the field.

Design Hierarchy

Searches your Design Hierarchy; results appear in the Search window.

Find All: Displays all finds in the Search window.

Stimulus Hierarchy

Searches your Stimulus Hierarchy; results appear in the Search window.

Find All: Displays all finds in the Search window.

Log Window

Searches your Log window; results are highlighted in the Log window - they do not appear in the Search Results window.

Find All: Highlights all finds in the Log window.

Next: Proceed to next instance of found text.

Previous: Proceed to previous instance of found text.

Reports

Searches your Reports; returns results in the Reports window.

Find All: Highlights all finds in the Reports window.

Next: Proceed to next instance of found text.

Previous: Proceed to previous instance of found text.

Files

Searches your local project file names for the text in the Search field; returns results in the Search window.

Find All: Lists all search results in the Search window.

Files on disk

Searches the files' content in the specified directory and subdirectories for the text in the Search field; returns results in the Search window.

Find All: Lists all finds in the Search window.

File Type: Select a file type to limit your search to specific file extensions or choose *.* to search all file types.

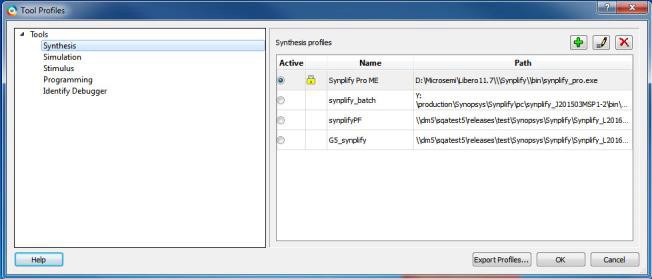

5.13.25 Organize Source Files Dialog Box – Synthesis

(Ask a Question)The Organize Source Files dialog box enables you to set the source file order in the Libero SoC.

Click the Use list of files organized by User radio button to add/remove source files for the selected tool.

To specify the file order:

- In the Design Flow window under Implement Design, right-click Synthesize and choose Organize Input Files > Organize Source Files. The Organize Source Files dialog box appears.

- Click the Use list of files organized by User radio button to Add/Remove source files for the selected tool.

- Select a file and click the add or remove buttons, as necessary. Use the Up and Down arrows to change the order of the Associated Source files.

- Click OK.

5.13.26 SmartDesign Testbench

(Ask a Question)SmartDesign testbench is a GUI-based tool that enables you to design your testbench hierarchy. Use SmartDesign testbench to instantiate and connect stimulus cores or modules to drive your design.

You can create a SmartDesign testbench by right-clicking a SmartDesign component in the Design Hierarchy and choosing Create Testbench > SmartDesign. SmartDesign testbench automatically instantiates the selected SmartDesign component into the Canvas. You can also double-click Create SmartDesign Testbench in the Design Flow window to add a new SmartDesign testbench to your project. New testbench files appear in the Stimulus Hierarchy. SmartDesign Testbench automatically instantiates your SmartDesign component into the Canvas.

You can instantiate your own stimulus HDL or simulation models into the SmartDesign Testbench Canvas and connect them to your DUT (design under test). You can also instantiate Simulation Cores from the Catalog. Simulation cores are simulation models (such as DDR memory simulation models) or basic cores that are useful for stimulus generation (such as Clock Generator, Pulse Generator, or Reset Generator). Click the Simulation Mode check box in the Catalog to view available simulation cores. Refer to the SmartDesign User Guide for more information.

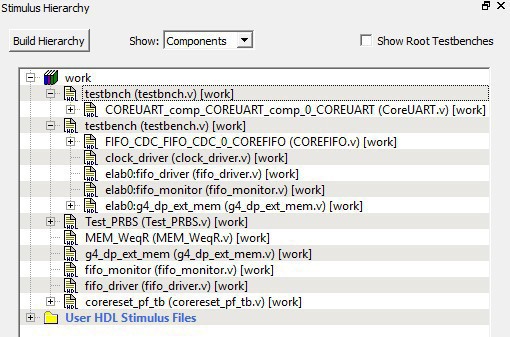

5.13.27 Stimulus Hierarchy

(Ask a Question)To view the Stimulus Hierarchy, from the View menu choose Windows > Stimulus Hierarchy.

The Stimulus Hierarchy tab displays a hierarchical representation of the stimulus and simulation files in the project. The software continuously analyzes and updates files and content. The tab in the following figure displays the structure of the modules and component stimulus files as they relate to each other.

Expand the hierarchy to view stimulus and simulation files. Right-click an individual component and choose Show Module to view the module for only that component.

Select Components, instance or Modules from the Show drop-down list to change the display mode. The Components view displays the stimulus hierarchy; the modules view displays HDL modules and stimulus files.

The file name (the file that defines the module or component) appears in parentheses. Click Show Root Testbenches to view only the root-level testbenches in your design.

Right-click and choose Properties; the Properties dialog box displays the pathname, created date, and last modified date.