3.5.1.27 Instantiating SmartHLS IP Core in Libero

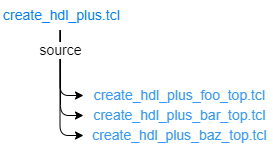

(Ask a Question)After we use SmartHLS to design a hardware IP component, we will want to instantiate the component into Libero and integrate this core into our larger system. When SmartHLS generates the hardware, SmartHLS will also generate (under hls_output/scripts directory) a root create_hdl_plus.tcl script and one create_hdl_plus_<top_level>_top.tcl script for each top-level function in your C++ design. These scripts can be used to easily instantiate the SmartHLS-generated IP core(s) into Libero. For example, let's say we have a design with 3 top-level functions foo, bar, and baz. The root create_hdl_plus.tcl is used to source all top-level specific HDL+ scripts:

-

create_hdl_plus_foo_top.tcl -

create_hdl_plus_bar_top.tcl -

create_hdl_plus_baz_top.tcl

If you want to instantiate all 3 SmartHLS-generated IP cores in Libero, you can run the root create_hdl_plus.tcl. Otherwise, if you only want to instantiate a single IP core of a particular top-level e.g. foo, you can run just run the create_hdl_plus_foo_top.tcl.

Now, let's consider a simple example with only one top-level sobel_filter() to demonstrate how you can run the tcl script. Firstly, when SmartHLS finishes generating the hardware, you will see the log message in the console which includes the full path to the root create_hdl_plus.tcl like this:

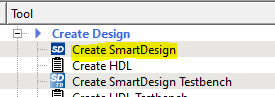

Info: Generating HDL+ Tcl script to be imported in SmartDesign: C:\Users\<username>\hls_workspace\sobel_part3\create_hdl_plus.tcl.Now we can use Libero to open a Libero project, create a new SmartDesign, and give the newly created SmartDesign a suitable name. Alternatively, we can also open an existing SmartDesign.

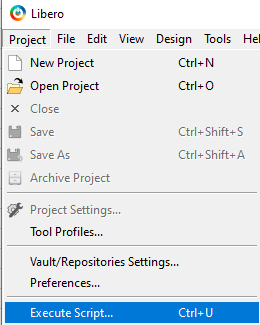

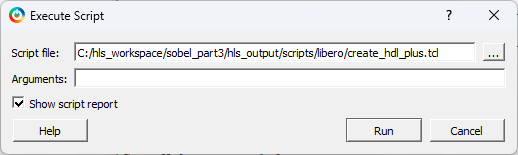

We now go to the Libero Project menu and select Execute Script and give the path to the generated create_hdl_plus.tcl script as shown in the figures below. Then click Run. Running the Tcl script will add the SmartHLS-generated HDL+ component (sobel_filter_top in this example), all required Verilog files, memory initialization files, and other dependencies to the Libero project. Alternatively, because this design only has 1 top-level, running the top-level specific create_hdl_plus_sobel_filter_top.tcl will achieve the same effect.

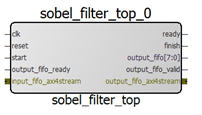

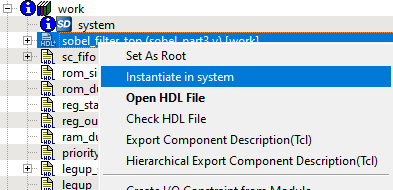

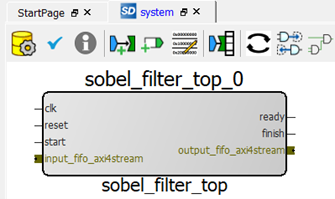

As shown in the figures below, we can now instantiate the component in SmartDesign by right-clicking on the HDL+ component (sobel_filter_top in this example) in the Design Hiearchy panel on the left and selecting Instantiate in system. In the SmartDesignsystem we will now see the new IP component (sobel_filter_top_0 in this example).

The generated create_hdl_plus_sobel_filter_top.tcl script will automatically group ports as AXI4 Master, AXI4 Slave or AXI4 Stream interfaces if they match the corresponding AXI4 specifications. In this example, since the sobel_filter_top IP component used SmartHLS FIFOs as top-level arguments and they match AXI4 Stream specifications, SmartHLS has automatically grouped the output_fifo and input_fifo data/ready/valid ports as AXI4 Stream interfaces.

Similarly, if your top-level uses either AXI4 Initiator or AXI4 Target interfaces, the script will group all AXI4 Initiator signals axi4initiator_* into a bus, and all AXI4 Target signals axi4target_* into a bus, if applicable. (For more details about the different types of AXI4 interfaces, please refer to Top-Level RTL Interface).

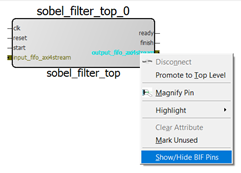

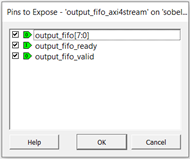

We also have the option to expose the sub-signals under the AXI4 bus. This will allow us to connect individual ports instead of the entire bus. To do this, right click on the AXI4 bus on the SmartHLS-generated IP component and choose Show/Hide BIF Pins. Then choose the sub-signals as appropriate. For example, in the figures below, if we choose all 3 sub-signals of the AXI4 Stream interface and press OK, we will see the 3 corresponding ports in the IP component: output_fifo_ready as an input, and output_fifo[7:0] and output_fifo_axi4stream as the outputs.