3.5.1.29 User-defined SmartDesign

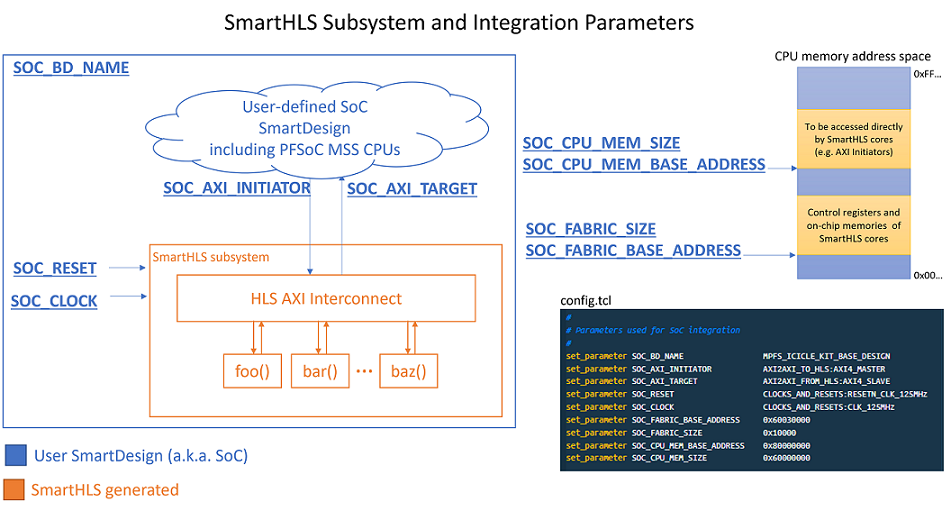

(Ask a Question)The automatic integration of SmartHLS™ cores can also be applied to user-defined SmartDesign, not just the Icicle Kit Reference Design included with SmartHLS as long as some integration parameters are specified as shown in the following image:

This image shows the integration parameters (underlined) that are used by SmartHLS to automate the integration of three hardware modules, in this example: foo(), bar() and baz(). These parameters have default values based on the Icicle_SoC reference design included in SmartHLS but can be overridden as necessary in the config.tcl file to adapt to user-defined designs.

The following table further describes the integration parameters:

| Parameter name | Default value | Description |

|---|---|---|

| SOC_BD_NAME | FIC_0_PERIPHERALS | The name of the SmartDesign project into which the SmartHLS IP modules will be integrated. |

| SOC_DMA_ENGINE | HARD_DMA | Determines the type of DMA engine to use. HARD_DMA: will use the DMA available in the PolarFire SoC MSS. This implies that the CPUs to be used are the RISC-V U54 application cores in the MSS. SOFT_DMA: will automatically instantiate a DMA engine on the FPGA fabric and be connected to the SmartHLS AXI interconnect along with the SmartHLS IP modules. Currently this option is not enabled, but will be in a future release. |

| SOC_AXI_INITIATOR | AXI2AXI_TO_HLS:AXI4_MASTER | Identifies the downstream AXI interface to use. This is used for register control and any data write and read transfers initiated by the CPU down to the SmartHLS IP modules. |

| SOC_AXI_TARGET | AXI2AXI_FROM_HLS:AXI4_SLAVE | Identifies the upstream AXI interface to use. This is used for write and read transfer requests issued by the SmartHLS IP modules targeting the CPU memory. |

| SOC_RESET | ARESETN | Identifies the reset signal to be used. Important: reset polarity must be active-High. |

| SOC_CLOCK | ACLK | Identifies the clock to use for the SmartHLS IP modules. Currently, the same clock is used for all modules. |

| SOC_FABRIC_BASE_ADDRESS | 0x70000000 | This is the base address of a memory window in the CPU memory address space that is reserved for all SmartHLS modules instantiated on the FPGA fabric. Control registers and on-chip memory buffers are allocated and mapped from this memory window. This address is also used to configure the HLS AXI interconnect to allow AXI transactions to move downstream from the CPU towards the SmartHLS IP modules. Important: The address is hexadecimal value and the ‘0x’ prefix must be included. |

| SOC_FABRIC_SIZE | 0x400000 | Determines the size of the memory window used for mapping control registers and on-chip buffers for ALL modules in a given SmartHLS project instantiated on the fabric. The size can be larger than what a specific function may need. For example, a 4MB memory window could be reserved but the IP module may only use half ot if, leaving the other half for future use. Reserving a larger window does not mean more on-chip memory will be used. Important: The size is a hexadecimal value and the ‘0x’ prefix must be included. |

| SOC_CPU_MEM_BASE_ADDRESS | 0x80000000 | This base address identifies the beginning of a memory window in the CPU physical memory address space that the SmartHLS IP modules can use when they are AXI Initiators. This address is used to configure the HLS AXI interconnect and allow transactions to move upstream towards the CPU’s memory. Important: The size is a hexadecimal value and the ‘0x’ prefix must be included. |

| SOC_CPU_MEM_SIZE | 0x60000000 | This is size of the CPU memory window used when the SmartHLS IP modules act as AXI initiators. Important: The size is a hexadecimal value and the ‘0x’ prefix must be included. |

| SOC_POLL_DELAY | 0 | Controls how often the hardware driver polls the modules to check for completion. The value is in microseconds. |

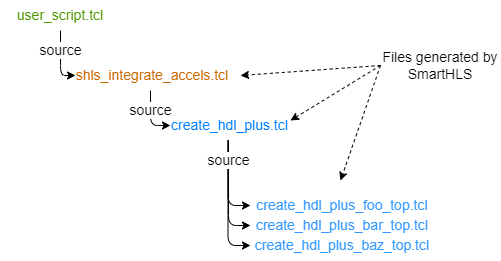

Once the SmartHLS IP modules have been generated, for example after running the command shls hw from the terminal, the generated RTL code for all modules can be integrated by sourcing the shls_integrate_accels.tcl script. This can be done from Libero's GUI or sourced from a user Tcl script:

The shls_integrate_accels.tcl can also be called from the command-line. For example, you can create a script like this:

user_script.tcl:

open_project -file path/to/my_project.prjx

source path/to/hls/project/hls_output/scripts/shls_integrate_accels.tcl

close_project -save 1Then on the terminal:

$> libero script:user_script.tcl

This will integrate all the SmartHLS IP modules into the user-defined project. After this, the system can be synthesized and run through place and route.