3.5.1.31 SmartHLS™ Command-Line Interface

(Ask a Question)In addition to the SmartHLS IDE, there is also a command-line tool (shls) available to call SmartHLS from a terminal, or from a user script for the purposes of automation.

Setup

To run SmartHLS from the command-line, your PATH environment variable should contain the paths to:

shls: SmartHLS executable.vsim: ModelSim’s executable for HW simulation and SW/HW co-simulation.libero: Liberos executable for synthesis and Place & Route.

For Windows, SmartHLS provides scripts for setting up

PATH environment variable for SmartHLS, Libero and ModelSim. These scripts can be found under SmartHLS-<version2024.2>\SmartHLS\bin.

You can either run the scripts manually in Powershell/Command Prompt/WSL to set up

the PATH variable, or you can use the SmartHLS IDE to do it automatically.

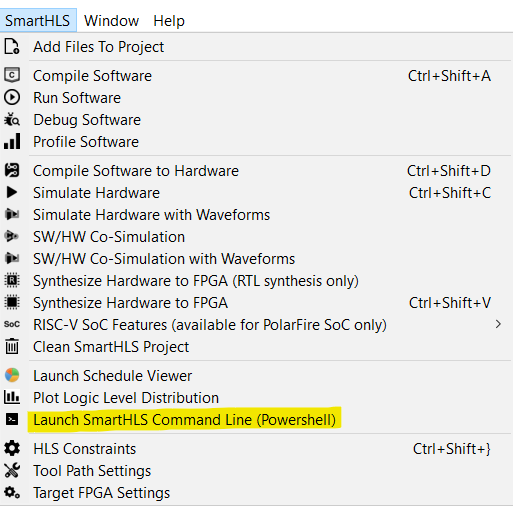

To do it automatically, in the Windows SmartHLS IDE, click

SmartHLS > Launch SmartHLS Command Line

(Powershell). This starts a Windows Powershell window with the

correct PATH setting.

Here’s an example that you can adapt to your system:

export PATH=<SMARTHLS_INSTALLATION_DIR>/SmartHLS/bin:$PATH

################################ For Windows ################################

export PATH= <LIBERO_SOC_INSTALLATION_DIR>/QuestaSim/win64:$PATH

export PATH=<LIBERO_SOC_INSTALLATION_DIR>/Designer/bin:$PATH

################################# For Linux #################################

export PATH=<LIBERO_SOC_INSTALLATION_DIR>/QuestaSim/questasim_mcoem/bin:$PATH

export PATH=<LIBERO_SOC_INSTALLATION_DIR>/Libero/bin64:$PATHSmartHLS comes with a bash script to provide auto-completion when using the command-line on a Linux terminal. It can be sourced like this:

source <SMARTHLS_INSTALLATION_DIR>/SmartHLS/examples/scripts/utils/autocomplete/bash_autocomplete.shAfter that you can start typing shls plus a space, then hit the

<TAB> key and a list of available commands will be

displayed. If you continue typing the command and hit the

<TAB> key again the command will be auto-completed.

Commands

Here is the list of available commands:

shls [-h] <cmd>

Where <cmd> can be one of the following:

- init

Create a new SmartHLS project by generating a

Makefileand aconfig.tclfile.Makefile- this file has the following variablesSRCS: This variable should list all the source files (.cppor.c). Header files should not be added toSRCS, but should be properly included by the source files.shls initwill automatically add the file names for the existing source files in the current directory. If source files are created aftershls init, please updateSRCS(e.g.,SRCS = foo.cpp bar.cpp).NAME: This variable stands for the project name, e.g.,NAME = MY_PROJECT. The default project name is the current directory name whenNAMEis not specified inMakefile.PROGRAM_ARGUMENTS: This variable can be used to specify the arguments for the main() function, which can be used for the software testbench (i.e.,int main(int argc, char *argv[])). Here is an example:PROGRAM_ARGUMENTS = input_file.bmp golden_output_file.bmp. More details can be found in SW/HW Co-Simulation.

Important: The above variables should be specified before the last line inMakefile: include $(LEVEL)/Makefile.common.config.tcl- this file contains the project’s configuration settings. Project parameters and constraints can be specified in this file as necessary. Please refer to the Constraints Manual page.

- -g

- Launch SmartHLS IDE from command-line.

- sw

- Compile and run the program in software on your host machine. The compilation step is skipped if no change is detected in source/header files,

Makefileandconfig.tcl. - sw_compile

- Compile the program in software, the output is an executable file (

hls_output/.hls/<NAME>.sw_binary). - sw_run

- Run the compiled executable (

hls_output/.hls/<NAME>.sw_binary) on your host machine. - hw (default)

- Compile the software to hardware, the output is a set of Verilog HDL file (the HLS-generated IP core is in

hls_output/rtl/<NAME>.v, with additional RTL IP sub-modules namedhls_output/rtl/<NAME>_*.v). - cosim

- Run Simulate HLS Hardware (SW/HW Co-Simulation) to verify the generated circuit.

- cosim_wave

- Same as

cosimbut with ModelSim waveform. - sim

- Simulate the generated hardware in ModelSim (for an input software that has no top-level function specified, which is uncommon).

- wave

- Same as above but with ModelSim waveform.

- fpga

- Synthesize the generated hardware to target FPGA. This runs RTL synthesis and place-and-route for resource and timing results.

- rtl_synth

- Run RTL synthesis for resource results. This will take less time than fpga.

- scheduleviewer

- Show the scheduler viewer.

- logic_level_histogram

- Generates a plot of the logic levels distribution of the synthesized design based on the timing analysis report.

- clean

- Delete files generated by SmartHLS.

- instrument_init

- Generates the instrumentation configuration file

(

instrument_conf.json) in the SmartHLS project directory with some default values that can be adjusted manually by the user as required. For more information on the configuration file, see Configuration File. - soc_*

- SoC-specific commands are prefixed with “soc_” and are outlined in the table below:

| Command | Description |

|---|---|

| soc_base_proj_program | Programs a pre-built base project bit stream to an attached Icicle Kit. |

| soc_sw_compile_no_accel | Cross-compiles user software (with no accelerators) to a binary targeting the RISC-V processor on PolarFire® SoC. |

| soc_base_proj_run | Moves the RISC-V binary generated by soc_sw_compile_no_accel to an Icicle Kit on the network and runs the binary on the Icicle kit. Requires the BOARD_IP environment variable to be set. |

| soc_accel_proj_generate | Generates a reference SoC Libero/SmartDesign project, containing an MSS connected to SmartHLS™-generated hardware accelerators. Please see SmartHLS Reference SoCfor more information. |

| soc_accel_proj_rtl_synth | Runs RTL synthesis on the generated reference SoC project. Reports resource utilization (see Report Files). |

| soc_accel_proj_pnr | Runs place and route on the generated reference SoC project. Reports resource utilization and timing result (see Report Files). |

| soc_accel_proj_program | Programs the generated reference SoC project to an attached Icicle Kit. Requires PROGRAMMER_ID environment variable to be set. |

| soc_sw_compile_accel | Transforms user software by replacing top-level function calls with calls to the Top-level Driver Functions, and cross-compiles the transformed software to a binary targeting the RISC-V processor on PolarFire SoC. |

| soc_accel_proj_run | Moves the RISC-V binary generated by soc_sw_compile_accel to an Icicle Kit on the network and runs the binary on the Icicle kit. Requires the BOARD_IP environment variable to be set. |

| soc_profiler_view | Displays a runtime plot and prints a summary table of the profiling data gathered during runtime execution for each accelerator in the project. |