24.4.4.10 BUS RESET Generation

To prevent a malfunctioning device from locking up the I3C/Sideband bus, the I3C protocol and JEDEC Sideband Specifications define a bus protocol RESET mechanism. The Controller supports the generation of the following three standalone patterns:

- Timed Reset

- HDR-EXIT Pattern

- Target Reset Pattern

The Reset Pattern is selected in the I3CxRSTCON[RSTTYP] bits, and enable I3CxRSTCON[BUSRST] to generate the Reset. The Controller considers this request only when it is in the IDLE state and gives priority over scheduled regular commands. The Controller generates the selected Reset pattern based on the selection in I3CxRSTCON[RSTTYP].

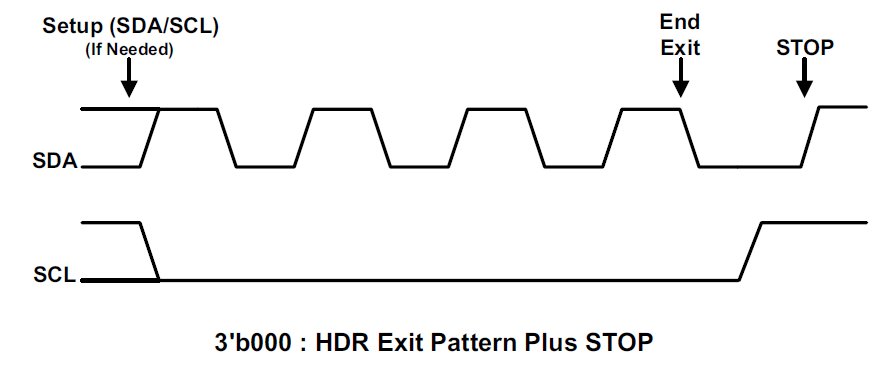

3'b000: HDR Exit Pattern

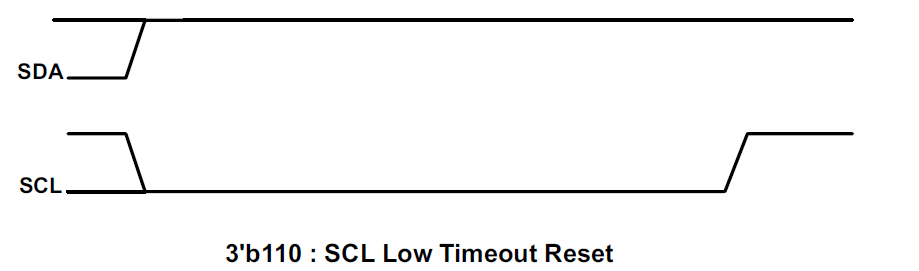

3'b110: Timed Reset (Drives SCL Low for the I3CxMSTTIMOUT [TIMOUTCNT] period of time)

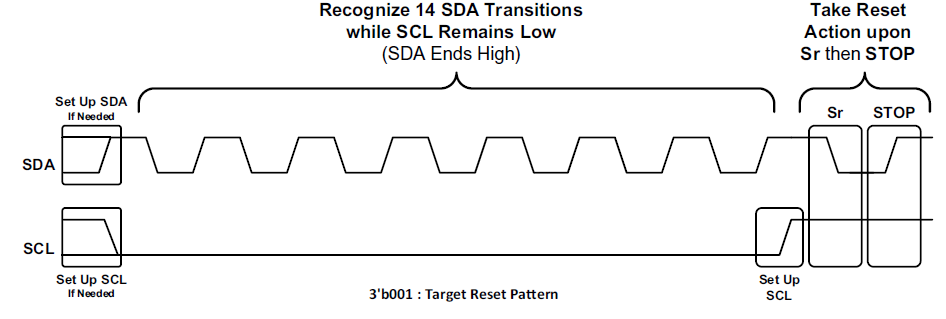

3'b001: Target Reset Pattern

Once the Controller completes the Requested Reset Pattern, the Controller auto-clears the I3CxRSTCON[BUSRST] request bit. The software can poll this request bit to know whether the Controller has completed the generation of the Requested Reset pattern. An interrupt is generated, indicating that the Request Reset pattern has been issued.

Figure 24-29, Figure 24-30 and Figure 24-31 show the SCL Timed Reset, HDR-EXIT Pattern and Target Reset Pattern, respectively.