12.4.1 Clock Generators (CLKGEN)

The dsPIC33A family of devices contains multiple clock generators. Each clock generator can be configured to use the input clock sources listed in Table 12-3. Clock generator 1 is the system clock, and it will always be enabled.

An expanded view of the CLKGEN is detailed in Figure 12-3.

The assignment of CLKGEN to peripherals is listed in Table 12-2.

The other clock generators can be configured for any clock source. For example, to reference FRC, set the COSC[3:0] bits to FRC source and enable clock switching.

Each generator can be enabled either via setting the ON bit in the CLKxCON register or when requested by a consumer (e.g. a peripheral).

The ON bit is logically ORed with clock request signals from other peripherals to enable the CLKGEN or PLL, and it can only be used to disable the CLKGEN or PLL when there are no active clock requests. In addition, clearing the OSCCTRL.PLLxEN bit disables PLLx.

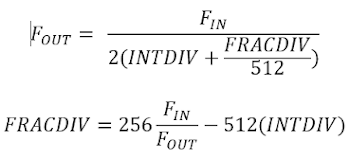

To calculate FOUT and FRACDIV refer to Equation 12-1

Each clock generator has a dedicated divider (CLKxDIV) and control bits.

CLK11CONbits.ON = 1; // Enable CLKGEN CLK11CONbits.OE = 1; // Enable output CLK11CONbits.NOSC = clkSource; // Clock source selection CLK11CONbits.OSWEN = 1; // Request clock switch while(CLK11CONbits.OSWEN); // Verify switch complete CLK11DIVbits.INTDIV = 2; CLK11CONbits.DIVSWEN = 1; // Request divider switch while(CLK11CONbits.DIVSWEN); // Verify switch complete while(!CLK11CONbits.CLKRDY); // Verify CLKGEN ready