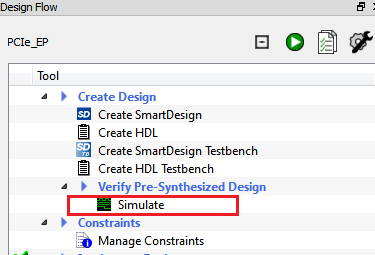

1.7 Simulating the Design

(Ask a Question)Before you begin, perform the following steps:

- Start Libero SoC in the Project menu, and click Open Project.

- Browse

mpf_an4597_df/HW/Eval_Kitormpf_an4597_df/HW/Splash_Kit. For simulation, create the Libero Project using provided TCL scripts. To create the Libero Project, see Appendix 4 : Running the TCL script section.

The PCIe BFM performs 1 KB DMA operations between PCIe and DDR3L, DDR4 and LSRAM memories by initiating AXI burst transactions. The PCIe BFM simulation model replaces the entire PCIe EndPoint interface with a simple BFM that can send write transactions and read transactions over the AXI interface. These transactions are driven by a script file (.bfm) and allow easy simulation of the FPGA design connected to a PCIe interface. For more information about BFM commands, see PolarFire Family PCI Express User Guide . The micron DDR3L and DDR4 memory models are instantiated in the testbench for simulating DDR3L and DDR4 memory controllers.