1.3.2.5 64b67b Transmit

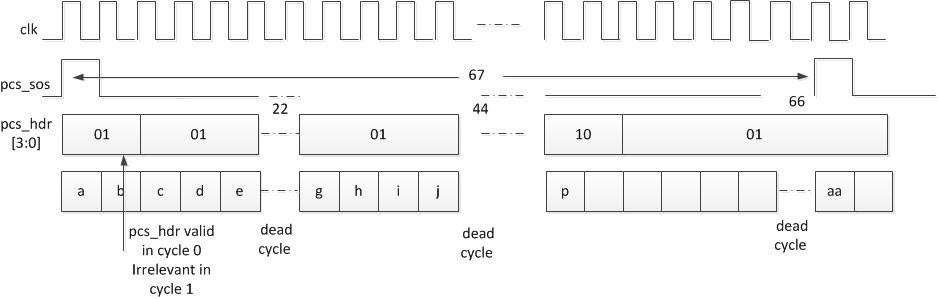

(Ask a Question)In the recommended configuration for 64b67b, encoded and scrambled data is presented from the fabric into TX_DATA along with sync headers on TX_HDR[3:0]. The data from the fabric must conform to the expected sequence of clock beats according to the fabric interface width.

The 64-bit interface option has dead cycles on clock beats 44, 45, 88, 89, 132, and 133.

The transmit data first enters the PCS Timing control block, which generates the appropriate markers for 64b67b blocks. The data then goes to the disparity calculation block. The total number of ones and zeros are balanced by inverting blocks as necessary. When a block is inverted, sync header bit 2 is set to mark the inversion. Bits [1:0] of the sync header have the same meaning as they do in 64b66b blocks.

Data from the disparity block then goes to the transmit gearbox where it is output in 32-bit chunks per clock beat and sent to the PMA serializer.