3.5.1.19.10 Standard C Library Assertions (assert.h)

(Ask a Question)The assertion support enables the SmartHLS™ to convert the assertion statements in .cpp to the equivalent checking logic in Verilog.

If you write the following code in the input .cpp file:

will generate the following Verilog with a $fatal statement.

// Unsynthesizable Statements

// synthesis translate_off

always @(posedge clk)

if (...) begin

// Terminate simulation and print diagnostic message with level 1

$fatal(1, "[%s:%d] (a < b) failed to be met!\n",`__FILE__, `__LINE__ );

end

end

// synthesis translate_onImportant: SmartHLS will optimize away assertion statements that are always True at compile time.

User Example

Given a test program where the assertion evaluates to False, the assertion failure will be caught in SW/HW Co-simulation.

Let's use the C++ code below as the example input for SmartHLS to synthesize:

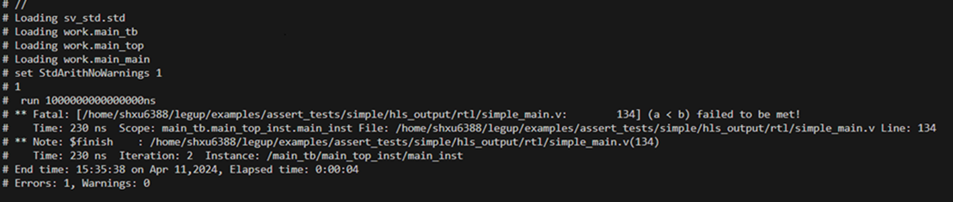

When we run SW/HW Co-simulation, the assert will fail and print the following information for the designers to troubleshoot:

- RTL file location and line number

- Assertion expression that triggered the failure