1.5.4.3 Jitter Attenuator

(Ask a Question)All transmit PLLs support a jitter-attenuator option. The jitter attenuator is used to track the data rate of any noisy reference clock with a clean input reference clock to provide a 0 ppm offset from the noisy reference clock while providing a jitter-cleaned output. It is used in designs requiring loop-timing where the recovered clock is used as the transmit clock requiring low jitter performance. This is used in applications such as Synchronous Ethernet (SyncE) providing low jitter synchronization to an Ethernet network. The following figure illustrates the application using jitter attenuation.

The TXPLL in the transceiver can provide jitter attenuation. Its design attenuates input jitter by using Libero configured settings to adjust the loop bandwidth and damping factors. The TXPLL input from the recovered source of the RX_CLK is cleaned from jitter components in the JA_CLK input path of the TXPLL. The TXPLL configurator allows pre-determined configurations of the attenuation feature based on protocol including the following protocols.

- 10G SyncE (32-bit, 64-bit)

- 1G SyncE 10-bit

- CPRI Rate [1-8]

- SDI (3G, HD, SD)

JA_PLL demonstrates compliance with the 10G SyncE the ITU-T G.8261 and G.8262 standards. A 10G SyncE Characterization Report and Libero Reference Design solution is available.

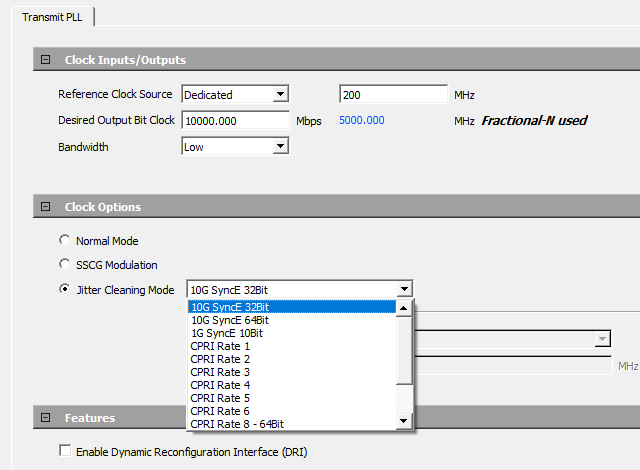

Select Jitter Cleaning Mode under the Clock Options and choose the targeted protocol templates from the drop-down as shown in the following figure.

Jitter attenuation PLL presets can be selected with TX PLL configurator (and the enable JA_CLK port in XCVR configurator). Jitter attenuation presets must follow the predefined requirements for the application design.

For example, if SDI 3G is selected in the TX PLL configurator, then set the PCS-FABRIC width in XCVR configurator to 20-bit and use the defined reference clock frequency.

| Jitter Cleaning Mode Selection | Data Rate (Mbps) | Reference Clock Frequency (MHz) | PCS - Fabric bit Width | Mode |

|---|---|---|---|---|

| 10G SyncE 32Bit | 10312.5 | 156.25 | 32 | 64b66b |

| 10G SyncE 64Bit | 10312.5 | 156.25 | 64 | 64b66b |

| 1G SyncE 10Bit | 1250 | 125 | 10 | PMA |

| CPRI Rate 1 | 614.4 | 122.88 | 32 | 8b10b |

| CPRI Rate 2 | 1228.8 | 122.88 | 32 | 8b10b |

| CPRI Rate 3 | 2457.6 | 122.88 | 32 | 8b10b |

| CPRI Rate 4 | 3072 | 122.88 | 32 | 8b10b |

| CPRI Rate 5 | 4915.2 | 122.88 | 32 | 8b10b |

| CPRI Rate 6 | 6144 | 122.88 | 32 | 8b10b |

| CPRI Rate 8 64-Bit | 10137.6 | 122.88 | 64 | 64b66b |

| SDI 3G | 2970 | 148.5 | 20 | PMA |

| SDI HD | 1485 | 148.5 | 10 | PMA |

| SDI SD | 270 | 148.5 | 10 | PMA |

| Custom Protocol Settings | See the following details. | |||