3.2.26 DIAG_TC

The DIAG_TC module is designed to verify the correct functionality of the Timer Controller (TC) through a set of C function calls.

The DIAG_TC software test API is mapped to the following safety mechanisms:

| Function | Diagnostic Mechanism | UseCase | Elasped Timer (μs) ~ |

|---|---|---|---|

| DIAG_TC_Disable() | TC_DISABLE | POST / OnDemand | 18 |

| DIAG_TC_DMA() | TC_DMA | POST / OnDemand | 11.22 |

| DIAG_TC_Enable() | TC_ENABLE | POST / OnDemand | 33 |

| DIAG_TC_Interrupts() |

TC_INTERRUPTS | POST | 49.20 |

| DIAG_TC_RedundantTimer() | TC_REDUNDANT_TIMER | POST / OnDemand | 45.62 |

| DIAG_TC_SFRReset() | SFR_RESET | POST | 52 |

| DIAG_TC_SFRWriteRead() | SFR_WRITE_READ | POST / OnDemand | 69 |

| DIAG_TC_SyncBusy() | TC_SYNCBUSY | POST / OnDemand | 20.32 |

#define TC_HW_LOOP_CNTR 0xF0U

#define TC_MAX_CLOCKS_DIFF 0x5U

typedef enum

{

DISABLE = 0,

TC0_OVF = 0x1B,

TC1_OVF = 0x1E,

TC2_OVF = 0x21,

TCC0_OVF = 0x10,

TCC1_OVF = 0x15,

TCC2_OVF = 0x18,

}DIAG_DMA_TRIGGER_SRC;

typedef enum diag_tc_nums

{

DIAG_TC0_NUM = 0,

DIAG_TC1_NUM = 1,

DIAG_TC2_NUM = 2,

DIAG_TC_MAX = 3,

}DIAG_TC_NUMBERS;

typedef enum diag_tc_periphs

{

DIAG_TC0_PERIPH = 1<<DIAG_TC0_NUM,

DIAG_TC1_PERIPH = 1<<DIAG_TC1_NUM,

DIAG_TC2_PERIPH = 1<<DIAG_TC2_NUM,

}DIAG_TC_PERIPHS;

typedef struct

{

bool ovf_set;

bool ovf_clrd;

bool cb;

}tc_int_status;

#define DIAG_TC_PERIPHS_CHECK_VALUE ((uint32_t)DIAG_TC0_PERIPH | (uint32_t)DIAG_TC1_PERIPH | (uint32_t)DIAG_TC2_PERIPH)

// *****************************************************************************

// *****************************************************************************

// Section: Data Types

// *****************************************************************************

// *****************************************************************************

// TC0<->TCC0 variables

extern uint32_t tc0_cntr, tc0_curr_cntr, tc0_prev_cntr, tcc0_cntr, tcc0_curr_cntr;

extern uint32_t tcc0_prev_cntr, tc0_tcc0_curr_diff, tc0_tcc0_prev_diff;

// TC0 interrupt status

extern tc_int_status tc0_ints;

// TC1<->TCC1 variables

extern uint32_t tc1_cntr, tc1_curr_cntr, tc1_prev_cntr, tcc1_cntr, tcc1_curr_cntr;

extern uint32_t tcc1_prev_cntr, tc1_tcc1_curr_diff, tc1_tcc1_prev_diff;

// TC1 interrupt status

extern tc_int_status tc1_ints;

// TC2<->TCC2 variables

extern uint32_t tc2_cntr, tc2_curr_cntr, tc2_prev_cntr, tcc2_cntr, tcc2_curr_cntr;

extern uint32_t tcc2_prev_cntr, tc2_tcc2_curr_diff, tc2_tcc2_prev_diff;

// TC2 interrupt status

extern tc_int_status tc2_ints;

Configuring the Diagnostic

DIAG_TC does not require additional configuration.

Configuring the System

Run-time Pre-requisites

DIAG_DIAG_TC_SFRWriteRead should be executed before DIAG_TC_SyncBusy, DIAG_TC_DMA and DIAG_TC_RedundantTimer

Using the Diagnostic

#include "definitions.h"

DIAG_TEST_STATUS DIAG_TC_SFRPost ( DIAG_TC_PERIPHS tc_periph )

{

DIAG_TEST_STATUS result;

result = DIAG_TC_SFRReset(tc_periph,NULL,0,false);

if (result == DIAG_TEST_PASSED)

{

result = DIAG_TC_SFRWriteRead(tc_periph,NULL,0,false);

}

return result;

}

DIAG_TEST_STATUS DIAG_TC_Post ( DIAG_TC_PERIPHS tc_periph )

{

DIAG_TEST_STATUS result;

result = DIAG_TC_Enable( tc_periph );

if( result == DIAG_TEST_PASSED )

{

result = DIAG_TC_Disable( tc_periph );

if( result == DIAG_TEST_PASSED )

{

result = DIAG_TC_SyncBusy( tc_periph );

if( result == DIAG_TEST_PASSED )

{

result = DIAG_TC_Interrupts( tc_periph );

if( result == DIAG_TEST_PASSED )

{

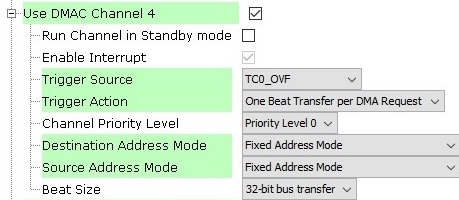

result = DIAG_TC_DMA( tc_periph, DMAC_CHANNEL_4 ); // must match DMA channel set up in MCC

if( result == DIAG_TEST_PASSED )

{

result = DIAG_TC_RedundantTimer( tc_periph );

}

}

}

}

}

return result;

}