3.5.1.24.3 Running SoC Features

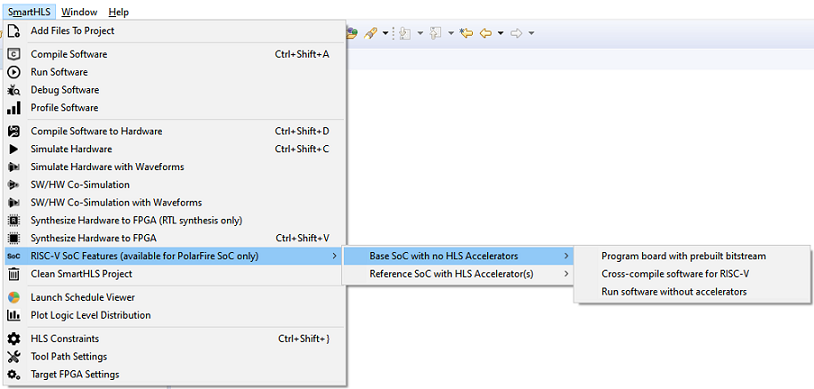

(Ask a Question)Base SoC Project Programming / Cross-Compilation

(Ask a Question)

In the same sub-menu, there is an option to cross-compile the project software into a binary for RISC-V (Cross-compile software for RISC-V), as well as an option to move this binary to an attached Icicle Kit and run it (Run software without accelerators). In order to run software on an attached Icicle Kit, some preliminary setup steps are required, see Icicle Kit Setup Instructions.

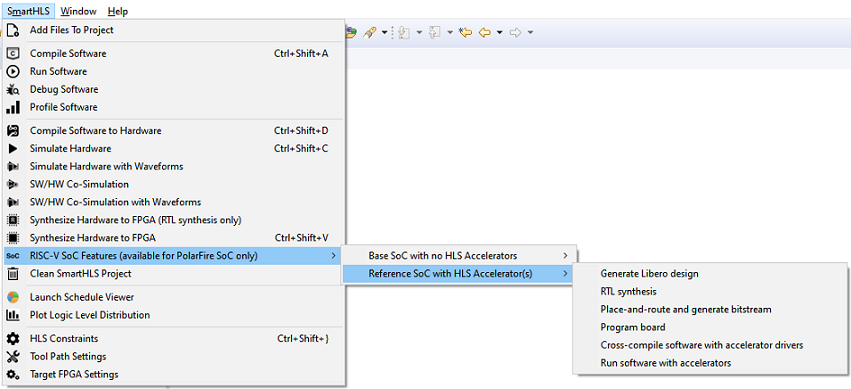

Reference SoC Generation

(Ask a Question)SmartHLS™ is also capable of taking the hardware accelerators it generates, and integrating them with the Microprocessor Sub-System (MSS) on a PolarFire® SoC FPGA (currently only supports PolarFire SoC Icicle Kit to create a reference SoC design in SmartDesign. This is done by taking the base SoC project, adding hardware accelerators as SmartDesign HDL+ cores, and connecting the components using an AXI4 interconnect. To generate this reference SoC design, navigate to the SmartHLS tab, and select . For more information on the architecture of this reference SoC, see SmartHLS™ Reference SoC.

In order for accelerators to be automatically integrated into a reference SoC, they must have only AXI4 Target and AXI4 Initiator hardware interfaces. This can be accomplished by specifying the correct interface pragmas (see interface pragmas section in the Pragmas Manual). For more information on the accelerator hardware interface see Top-Level RTL Interface.

Running the Reference SoC

(Ask a Question)In the same sub-menu, there are also options to run synthesis and place and route for the reference SoC, which can be used to check timing and resource usage of each accelerator as well as the whole SoC. There are also options to generate a bitstream and program it to an attached Icicle Kit. Finally, the Run software with accelerators option combines the input software with the generated accelerator drivers, and creates a software binary that can run on Linux in the Icicle MSS and drive the SmartHLS™ accelerators on the fabric. In order to run software on an attached Icicle Kit, some preliminary steps are required, see Icicle Kit Setup Instructions. For an example on how to do this with the MiV_RV32 on the PolarFire® Video Kit, see PolarFire Video Kit Setup Instructions.