1.3.3.9 CORESPI_0

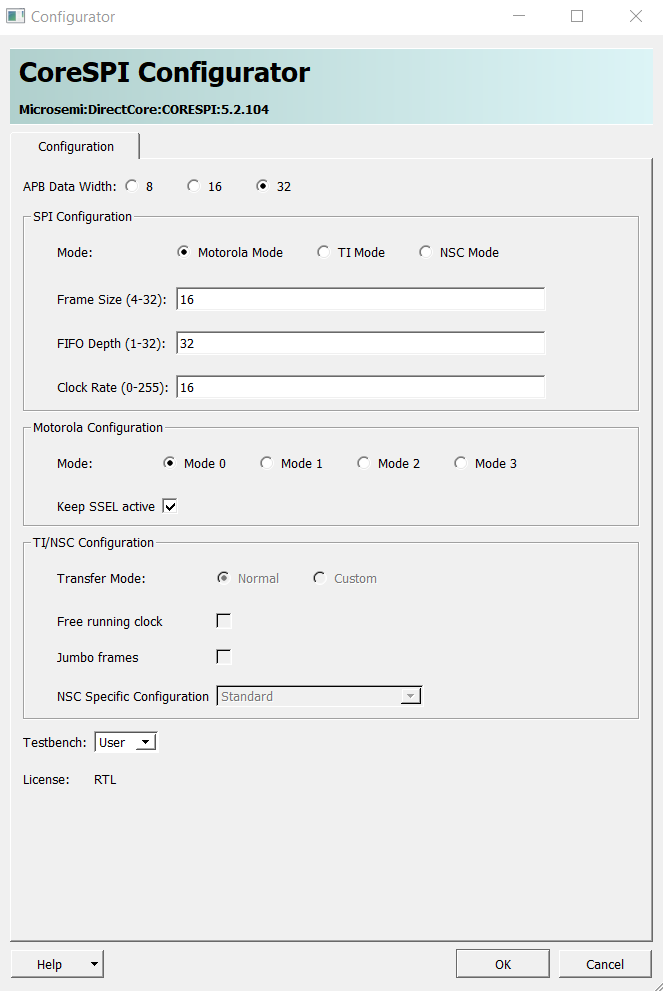

(Ask a Question)The CORESPI_0 (CoreSPI) block is a controller IP, which implements the SPI communication. Mi-V configures the ZL30364 clock generation hardware using the CORESPI_0 block. The following points describe the CoreSPI_0 configuration, as shown in Figure 1-10.

- APB Data Width is selected as 32 because the design uses 32-bit APB data width

- The default serial protocol mode, Motorola mode, is retained to interface with ZL30364

- Frame size is set to 16 to match the read/write cycles supported by ZL30364

- FIFO depth is set to 32 to store the maximum frames (TX and RX) in FIFO

- Clock rate for the SPI master clock is selected as 16. This is used to generate the SPI clock of 2.35 MHz (SPICLK = PCLK/(2*(clock rate+1) = 80/(2*(7+1)) = 2.35 MHz)

- The Keep SSEL active check box is enabled to keep the slave peripheral active between back-to-back data transfers

The following figure shows the CoreSPI configuration.