1.3.3.6 Mi-V Soft Processor

(Ask a Question)The Mi-V soft processor supports RISC-V processor-based designs. It configures the ZL30364 clock generation hardware through the CoreSPI IP and the VSC PHY through the CoreTSE MDIO interface. It also configures the CoreTSE registers using the APB interface.

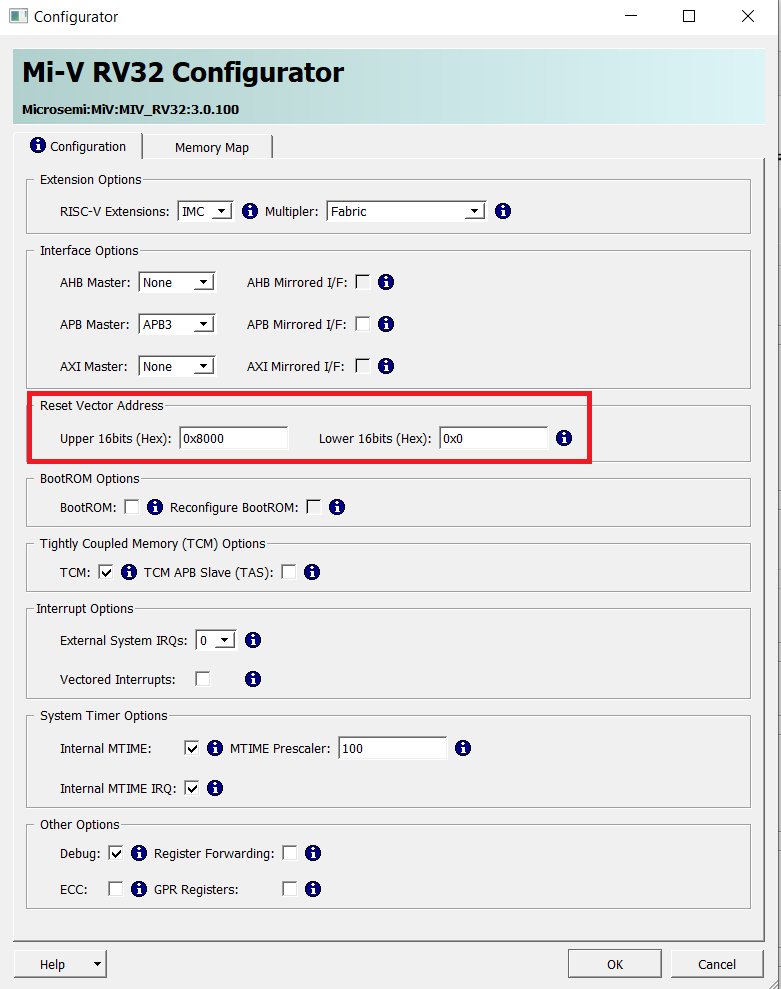

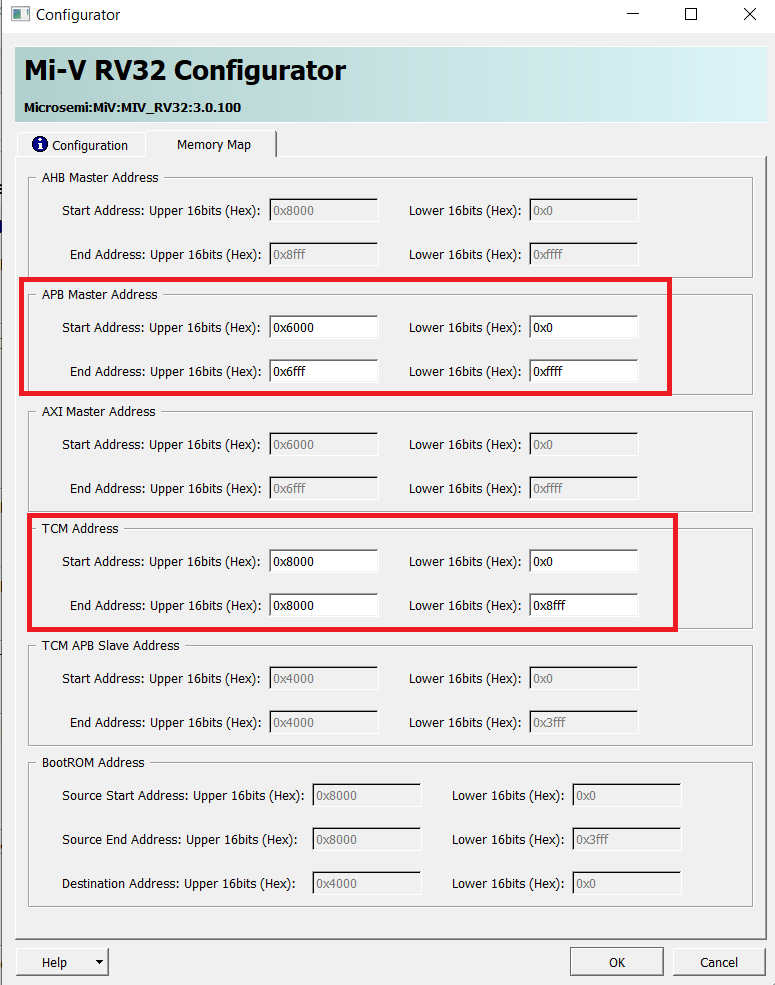

The following figures show the Mi-V soft processor configuration where the Reset Vector Address is set to 0x8000_0000. This is because in the Mi-V processor memory map, the memory range used for the APB interface is 0x6000_0000 to 0x6FFF_FFFF, and the memory range used for TCM is 0x8000_0000 to 0x8000_FFFF.