3.6.2.4.23 AXI_RRESP_ALWAYS_ZERO

(Ask a Question)The AXI_RRESP_ALWAYS_ZERO parameter determines how the HLS module will respond when it receives an AXI read requests to an address that is not used within its address map; essentially an address decoding error. These gaps within the addresses map occur due to address alignments in the AXI target register interface for the function arguments.

By default the module will return AXI RRESP=2'b10 (slave error) when an address decoding error is detected. It is the responsibility of the initiator of the AXI read request to process the response accordingly and the returned value (AXI RDATA) will be undefined although most likely it will be zero.

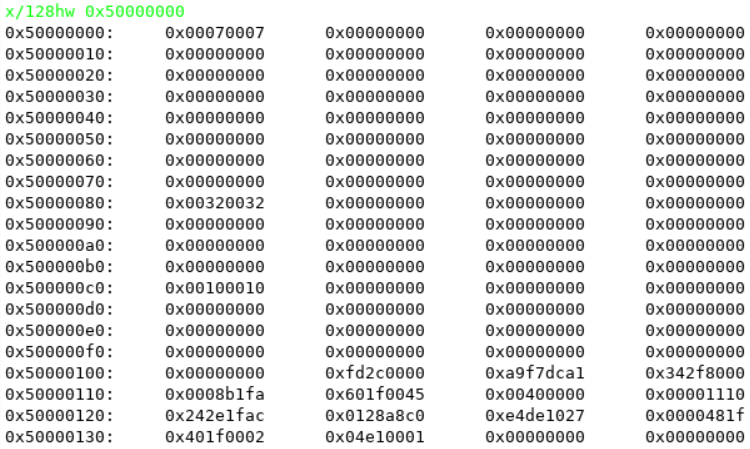

This response code can be forced to always zero by setting AXI_RRESP_ALWAYS_ZERO = 1 constraint, essentially ignoring any address decoding error. One reason to ignore this error is to perform memory monitoring or memory readout of the entire address space of a given HLS module for debugging purposes. This can be done in SoftConsole or with debuggers like gdb as can be seen in the following image using the command x/128hw 0x50000000, which means "read 128 words and print them in hex format starting at address 0x50000000", which would be the base address of the HLS module:

- Category

- HLS Constraint

- Value Type

- Boolean

- Valid Values

- 0, 1

- Default Value

- 0: disabled

- Location Where Default is Specified

examples/legup.tcl- Dependencies

- None

- Applicable Flows

- All devices and flows

- Test Status

- Alpha release

- Examples

set_parameter AXI_RRESP_ALWAYS_ZERO 1