12.4.4.2 Fractional Baud Rate Register

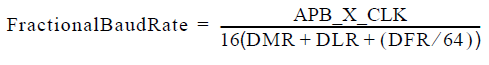

The baud rate divisor value is a 22-bit number consisting of a 16-bit integer and a 6-bit fractional part. This is used by the baud rate generator to determine the bit period. The fractional baud rate divider enables the use of any clock with a frequency >3.6864 MHz to act as input clock, while it is still possible to generate all the standard baud rates. The 16-bit integer is written to the integer baud rate register (Table 12-8). The 6-bit fractional part is written to the fractional baud rate register (Table 12-10). Table 12-10s are accomplished for divisor values greater than one using time averaging of the two nearest integer value baud rates based on the fractional value in the Table 12-8:

The special case of the integer divisor value (DLR+DMR) equal to one is not allowed in fractional mode as maximum error comes when the value is one. Therefore, use integer divisor values of two or more when using fractional mode.